# 1990 Product Catalog

1990 Product Catalog

| MODEL NUMBER                  | PAGE | MODEL NUMBER                 | PAGE |

|-------------------------------|------|------------------------------|------|

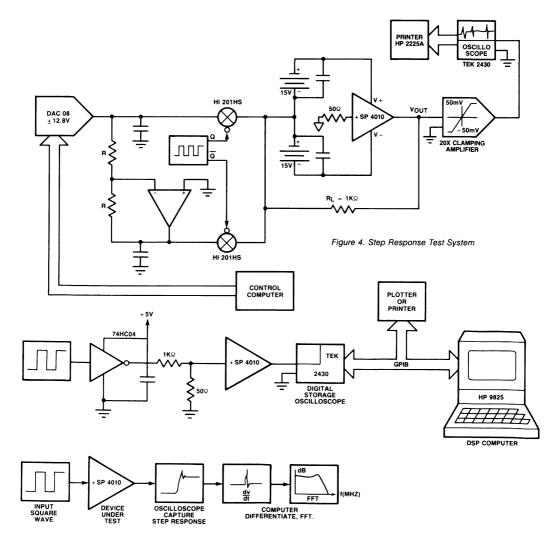

| ANALOG ARRAY PRODUCTS         | 2.2  | DAC338                       | 233  |

|                               |      |                              | 237  |

| SP1000 General Description    |      | DAC347                       |      |

| SP1104                        |      | DAC349                       | 237  |

| SP1204                        |      | DAC356                       | 243  |

| SP2107                        |      | DAC370-18                    | 245  |

| SP1000 Component Descriptions |      | DAC377-18                    | 247  |

| SP1000 Macro Cells            | 55   | SP1148                       | 251  |

|                               |      | H\$3020                      | 255  |

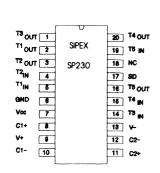

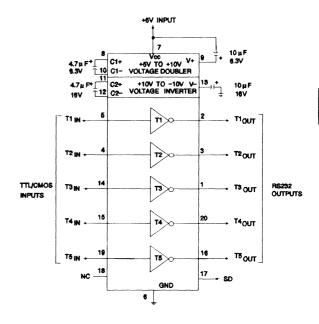

| RS232/422 INTERFACE PRODUCTS  | 75   | HS3120                       | 257  |

| SP230                         |      | HS3140                       | 261  |

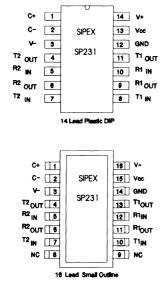

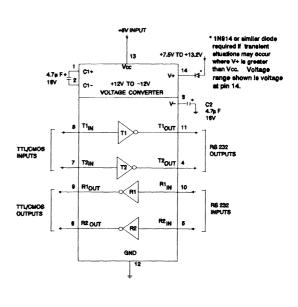

| SP231                         | 77   | HS3160                       | 263  |

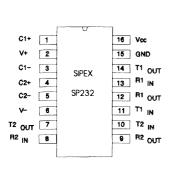

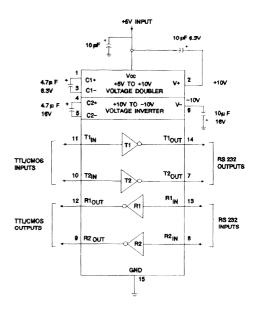

| SP232                         | 77   | HS3860                       | 269  |

| SP233                         | 77   | HS7541A                      | 273  |

| SP234                         |      | HS7584 (QUAD)                | 279  |

| SP235                         |      | SP9316                       | 291  |

| SP236                         |      | DAC9331-14                   | 299  |

| SP237                         |      | DAC9331-16                   | 299  |

| SP238                         |      | HS9338                       | 305  |

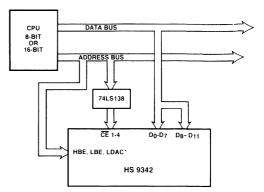

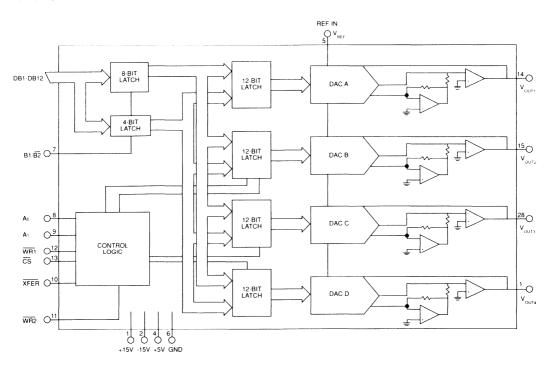

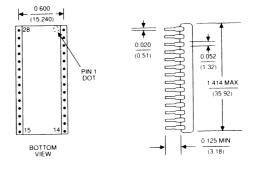

| SP239                         |      | HS9342 (QUAD)                | 309  |

| SP241                         |      | SP9344 (QUAD)                | 313  |

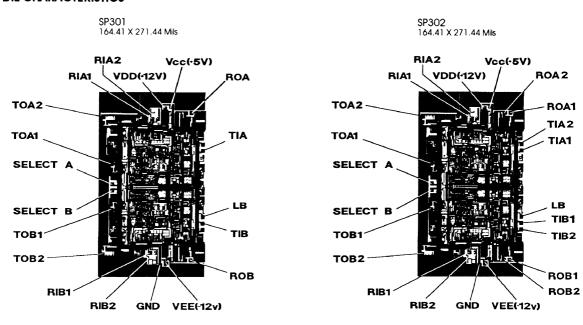

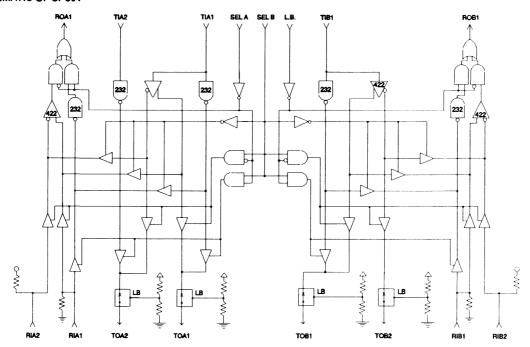

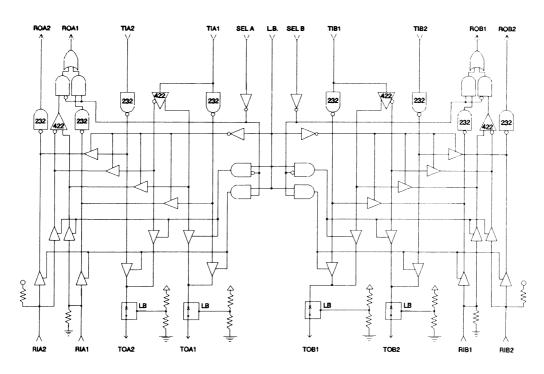

| SP301                         |      | DAC9349                      | 317  |

| SP302                         |      |                              | 319  |

| 3P30Z                         | 99   | DAC9356                      | 321  |

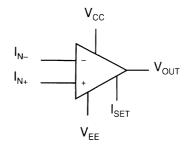

| OPERATIONAL AMPLIFIERS        | 07   | HS9371                       | 329  |

| SP111                         | ,,   | HS9372                       | 335  |

|                               | ,,   | DAC9377                      |      |

| SP121                         |      | HS9378                       | 339  |

| HS2020                        | 100  | SP9380                       | 345  |

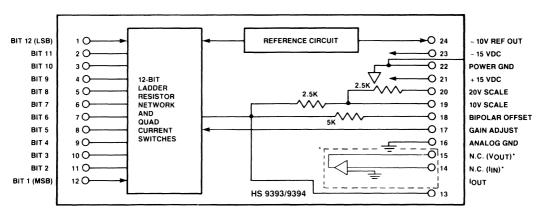

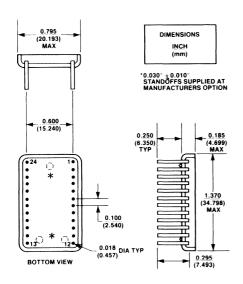

| SP2400                        | 107  | HS9393/94                    | 351  |

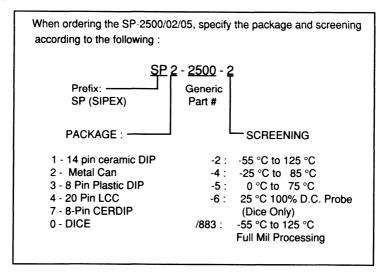

| SP2500                        |      | HS9390                       | 355  |

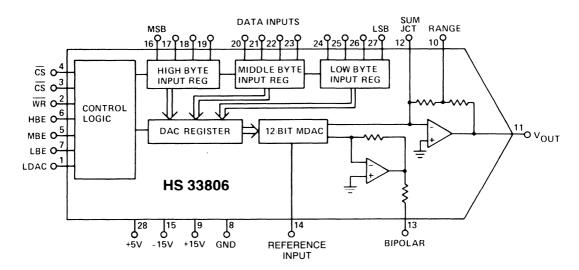

| SP2502                        |      | HS33806                      | 359  |

| SP2505                        |      |                              |      |

| SP2510                        | 117  | FLASH A/D SUBSYSTEMS         | 363  |

| SP2512                        | 117  | HS1068                       | 365  |

| SP2515                        | 117  | SP1070                       | 377  |

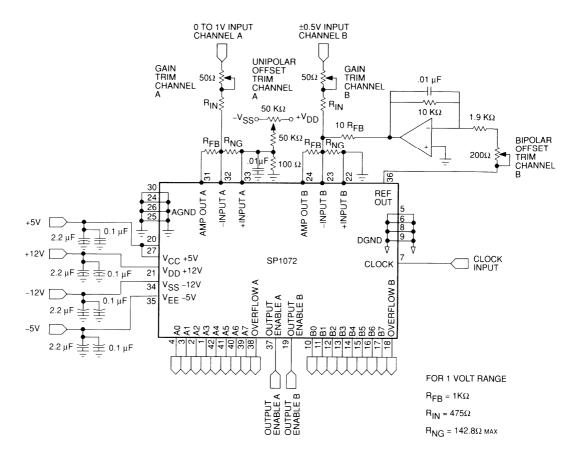

| SP2520                        | 123  | SP1072                       | 388  |

| SP2522                        | 123  | SP1078                       | 399  |

| SP2525                        |      |                              |      |

| SP2539                        |      | ANALOG-TO-DIGITAL CONVERTERS | 415  |

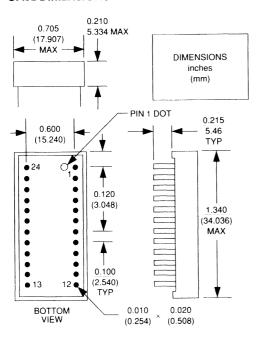

| SP2540                        |      | HS ADC82                     | 417  |

| SP2541                        |      | HS ADC85                     | 421  |

| SP2600                        |      | ADC541/542                   | 427  |

| SP2602                        |      | HS574A                       | 431  |

| SP2605                        |      | SP674A                       | 441  |

|                               |      | HS5131                       | 451  |

| SP2620                        | 141  |                              | 453  |

| SP2622                        |      | HS5150                       | 457  |

| SP2625                        | 141  | HS5210 Series                |      |

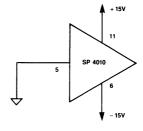

| SP4010                        | 147  | HS5251                       | 463  |

| SP5190/95                     | 155  | HS9516                       | 467  |

| SP9610                        | 159  | SP9548                       | 471  |

|                               |      | SP9550                       | 477  |

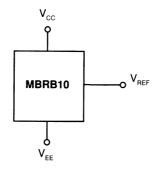

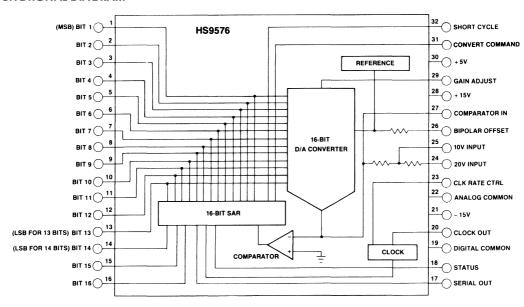

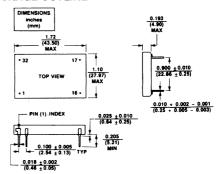

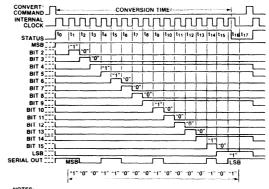

| VOLTAGE REFERENCES            | 163  | HS9576                       | 481  |

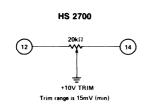

| HS2700                        | 165  | SP9588                       | 487  |

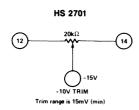

| HS2701                        | 165  |                              |      |

| HS2702                        | 165  | SAMPLING A/D CONVERTERS      | 491  |

|                               |      | HS9474                       |      |

| SAMPLE/HOLD AMPLIFIERS        | 169  | HS9476                       | 501  |

| HS346                         | 171  | SP9478                       | 509  |

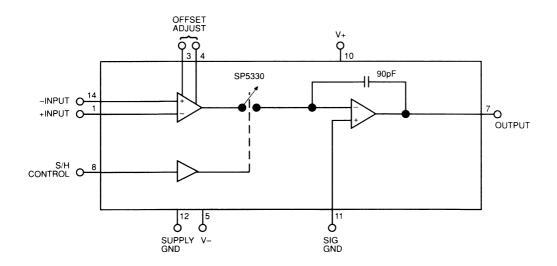

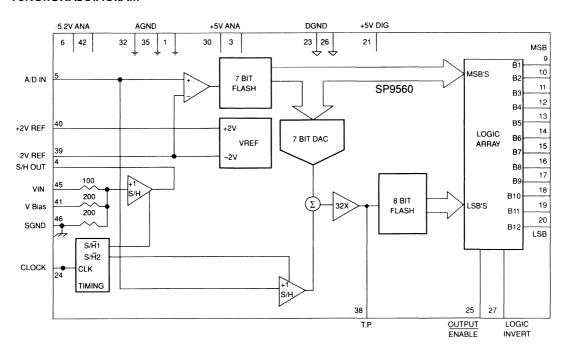

| SP5330                        | 173  | SP9560                       | 513  |

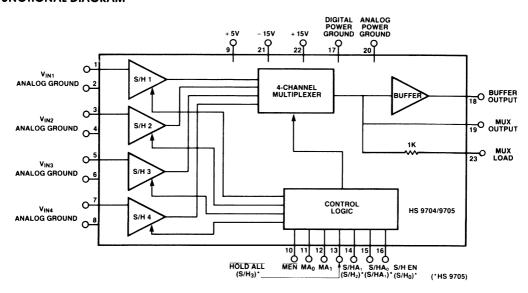

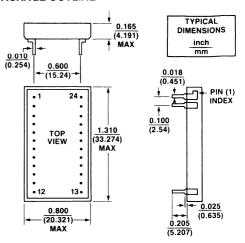

| HS9704/05 (QUAD)              | 177  |                              |      |

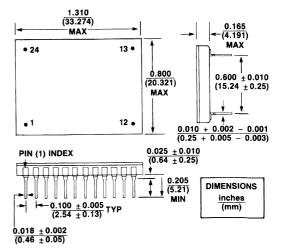

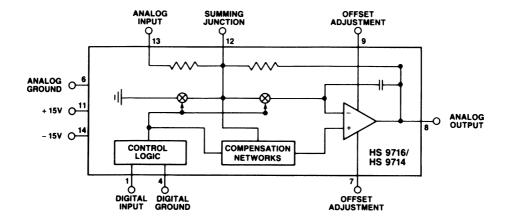

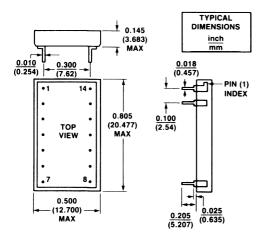

| HS9714                        | 181  | DATA ACQUISITION SYSTEMS     | 517  |

| HS9716                        | 181  | HS362                        |      |

| HS9720                        | 187  | HS9403                       |      |

|                               | 193  | HS9404/08                    |      |

| SP9730                        |      | HS9410                       | 535  |

| SP9760                        | 197  | HS9414                       |      |

| DICITAL TO ANIALOG CONVERTERS | 200  | SP9415                       |      |

| DIGITAL-TO-ANALOG CONVERTERS  | 209  |                              |      |

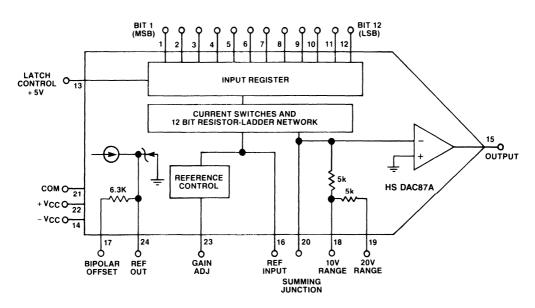

| DAC87                         | 211  | SP9462/63                    |      |

| DAC87A                        | 217  | SP9480                       |      |

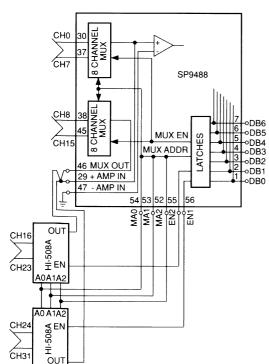

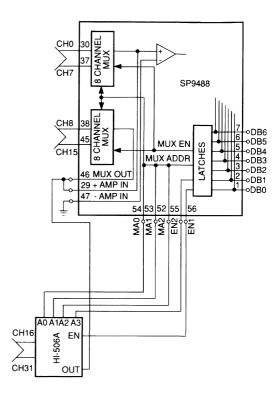

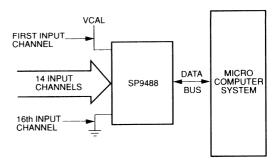

| DAC331                        | 223  | SP9488                       | 575  |

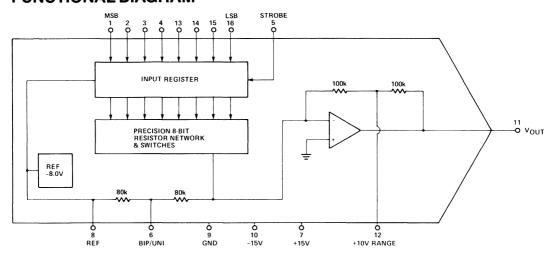

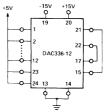

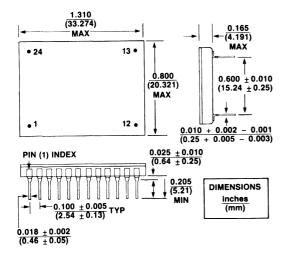

| DAC336-8                      | 225  |                              | 503  |

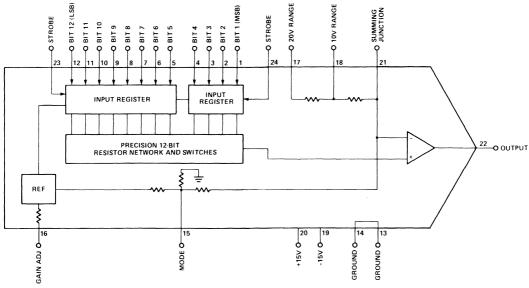

| DAC336-12                     | 225  | CUSTOM HYBRIDS               | 591  |

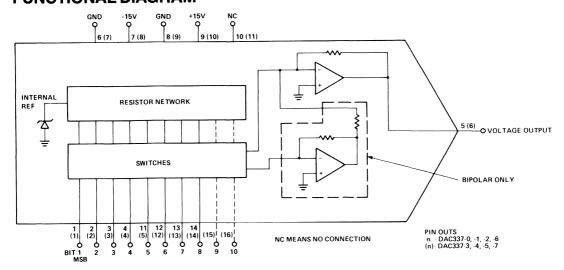

| DAC337                        | 231  |                              |      |

# **CONTENTS**

| SECTION | SUBJECT                                                                                                                                      | PAGE                    |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|         | PRODUCT LISTING                                                                                                                              | ii                      |

|         | CONTENTS                                                                                                                                     | iii                     |

|         | SIPEX INTRODUCTION                                                                                                                           | iv                      |

|         | MILITARY PROGRAMS                                                                                                                            | viii                    |

|         | Sales, Shipping and Service<br>Information                                                                                                   | ix                      |

|         | SALES OFFICE DIRECTORY                                                                                                                       | ×                       |

| 1       | APPLICATION NOTES  Selection Guide  Digitizing Dynamic Signals  Quad S/H Solves Acquisition  Problems  CMOS DACs  Analog Processing for Data | 1<br>2<br>3<br>11<br>17 |

|         | Acquisition                                                                                                                                  | 27                      |

| 2       | ANALOG ARRAY PRODUCTS                                                                                                                        | 33<br>34<br>35          |

| 3       | RS232/422 INTERFACE PRODUCTS                                                                                                                 | 75                      |

|         | Selection Guide<br>Product Data                                                                                                              | 76<br>77                |

| 4       | OPERATIONAL AMPLIFIERS Selection Guide Product Data                                                                                          | 97<br>98<br>99          |

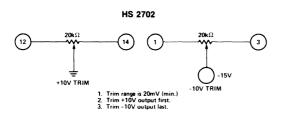

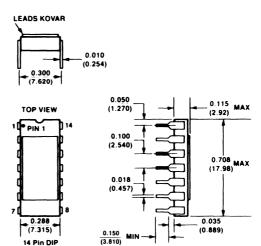

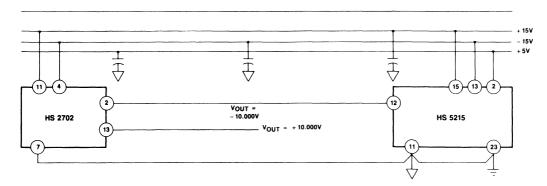

| 5       | VOLTAGE REFERENCES Selection Guide Product Data                                                                                              | 163<br>164<br>165       |

| 6       | SAMPLE/HOLD AMPLIFIERS                                                                                                                       | 189<br>170<br>171       |

| 7       | DIGITAL-TO-ANALOG CONVERTERS<br>Selection Guide<br>Product Data                                                                              | 209<br>210<br>211       |

| 8       | FLASH A/D SUBSYSTEMS Selection Guide Product Data                                                                                            | 363<br>364<br>365       |

| 9       | ANALOG-TO-DIGITAL CONVERTERS Selection Guide Product Data                                                                                    | 415<br>416<br>417       |

| 10      | SAMPLING A/D CONVERTERS  Selection Guide  Product Data                                                                                       | 491<br>492<br>493       |

| 11      | DATA ACQUISITION SYSTEMS Selection Guide Product Data                                                                                        | 517<br>518<br>519       |

| 12      | CUSTOM HYBRIDS                                                                                                                               | 591                     |

# SIPEX . . . EXCELLENCE IN SIGNAL PROCESSING

SIPEX is a manufacturing company that serves the analog signal processing market. The company produces signal conditioning, signal conversion and data acquisition system products utilizing both hybrid and monolithic technologies. Excelling in the fields of high speed and high precision, SIPEX offers products of standard, semicustom and full-custom design. SIPEX also produces and sells dielectrically isolated wafers

SIPEX's broad product offerings and capabilities are the result of recent mergers between Hybrid Systems Corporation, Datalinear Corporation Barvon and Dielectric Semiconductor Inc. As a result of the mergers, SIPEX provides its customers with multiple solutions to its signal processing needs.

produced to customer specifications.

While the name SIPEX is new, the foundations of the company represent years of solid technological achievements. SIPEX, which stands for Signal Processing Excellence, is the summation of the strengths of our two operations.

- East Coast, in operation for over twenty years, a leader in technological advances and certified to MIL-STD-1772, produces standard and custom hybrid circuits and thin film substrates.

- West Coast, designs and manufactures linear IC's and dielectric isolation base wafers, supplying military and commercial markets with full custom, standard, and ASIC products.

Quality and reliability have long been inherent to our company, consequently the wafers, IC's and hybrids manufactured by SIPEX are used in many major military and space programs including AMRAAM, Sparrow Missile, MILSTAR, Trident and SICBM. Industrially, SIPEX serves the ATE, process control, medical, seismics, telecommunications and other related market areas.

A unified worldwide sales network provides easy access to our capabilities and applications engineers. We are committed not only to the most advanced signal processing products, but also to the highest level of customer service.

#### **CERTIFIED TO MIL-STD-1772**

In addition to the standard hybrid and monolithic products shown in this catalog, Sipex offers the following additional capabilities:

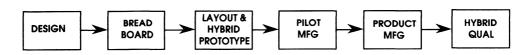

#### **CUSTOM HYBRID CIRCUITS**

In addition to having a complete line of standard products, Sipex Corporation also provides many complex application specific products to its customers.

Custom products include A/D converters, D/A converters, voltage to frequency converters, sample and holds, instrumentation amplifiers, OP amps, voltage references, multiplexers, modulators, filters, analog switches, bus interface, analog and digital interface, thin-film resistor networks, and thin-film substrates.

With state-of-the-art design and manufacturing equipment, Sipex Corporation is an industry leader in the manufacturing of custom hybrid components. Send your custom requirements to your Sipex representative or directly to the factory.

#### **CLASS "S" PRODUCTION**

Sipex's commitment to the highest achievable quality control and reliability is exemplified through Military/NASA standard Class "S" hybrids used in aerospace satellite and manned space flight applications. Sipex has dedicated a special program management office to control all Class "S" production. Our hybrids are being used in the space shuttle program, MILSTAR defense satellite, shuttle/centaur booster rocket, and various military classified defense satellites.

#### MIL-STD-1772

Sipex Corporation has been certified to produce Sipex Circuits which meet the requirements of MIL-STD-1772.

MIL-STD-1772 was established by the Defense Electronics Supply Center (DESC) to provide a standardized flow of fabrication processes and lines. It also provides for a standardization of Documentation and Testing.

Military Sipex Components purchased to MIL-STD-883 are now required to be manufactured and tested in a facility which is certified to MIL-STD-1772.

#### **RADIATION TESTING**

For the past several years, Sipex has been conducting in-house programs to study the effects of radiation on our converter products. Converter circuits have become an integral part of military and space programs and for these programs, radiation survivability is an essential factor. We have completed studies on precision reference sources, analog-to-digital and digital-to-analog converters using the facilities at the University of Lowell radiation laboratory. We have performed total exposure using CO-60 and fast neutron exposure using both an accelerator and a research reactor.

Sipex is willing and able to test for qualification any component which we manufacture and in addition, will be happy to quote on testing products from other manufacturers. Our experience testing and characterizing converter products makes us an ideal source for radiation testing.

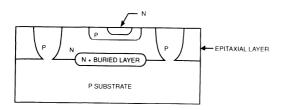

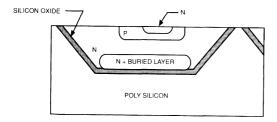

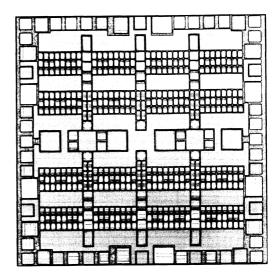

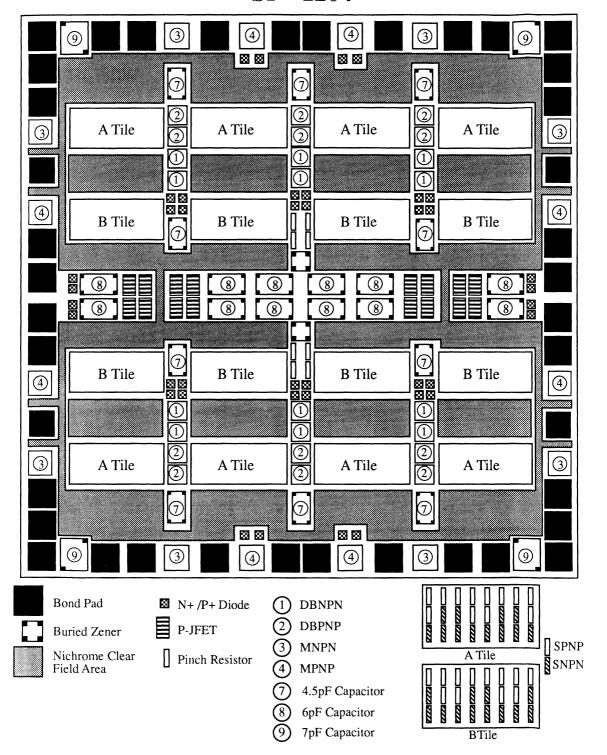

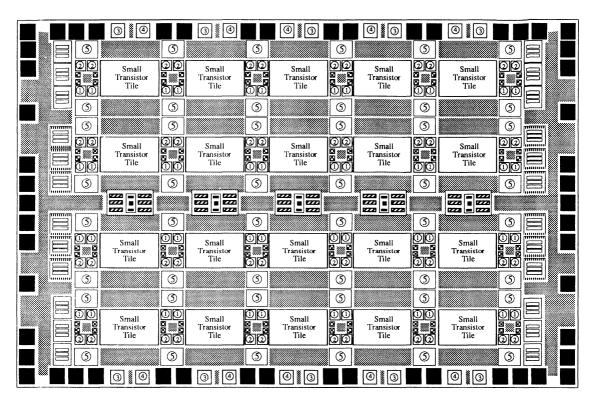

# DIELECTRIC ISOLATION TECHNOLOGY

# TECHNOLOGY/PRODUCTS

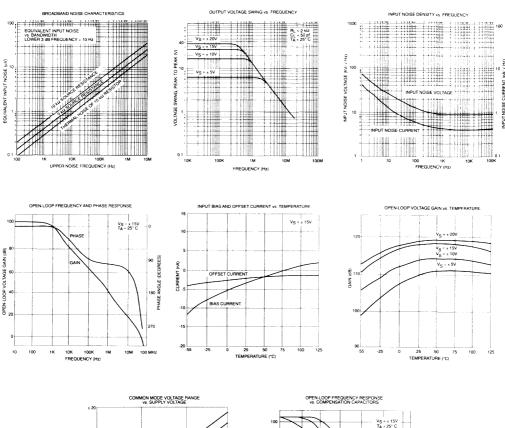

Sipex offers a broad range of high performance linear, monolithic IC's which either require or benefit from the use of Dielectric Isolation (DI) technology. This technology offers several significant user benefits:

- Higher bandwidths and slew rates than are achievable with conventional IC technology.

- High temperature operation (up to 200°C).

- Radiation hardened parts.

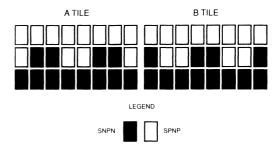

While DI has long been known for its radiation hardening benefits, its features extend beyond just radiation hardening. DI allows high  $f_T$ , vertical NPN and PNP bipolar transistors to be fabricated on the same chip. The presence of the high speed, vertical PNP transistor allows the high bandwidths, slew rates and settling times as well as the excellent DC characteristics that are uniquely associated with DI OP Amp type products.

Sipex's technology extends beyond just high speed, complementary transistors. In addition to these transistors and other devices, the IC processes employ p channel and n channel JFET's MOS capacitors, sub-surface zeners and

thin film Nichrome (NiCr) resistors. The NiCr resistors offer extremely low temperature coefficients and can be laser trimmed to achieve the ultimate in matching and precision. This library of devices offers users the best combination of speed and precision available on one chip today.

This DI technology can be accessed at one of four levels:

- Standard products

- Full custom

- Cell custom

- Array custom

#### **FACILITIES**

Sipex has a 31,000 sq. ft. building located in Milpitas, CA which houses a wafer fab, assembly and test operations, a design engineering staff, a full array of CAD/CAE equipment and other supporting staff and equipment. The wafer fab is Class 100 in the photo area and all work stations. The assembly line is MIL certified. Off-shore assembly houses have been selected and audited for supplying parts to cost sensitive operations.

Sipex also provides high quality dielectrically isolated silicon substrates to a broad spectrum of semiconductor manufacturers. Sipex provides unique structures in silicon that serve as a foundation for:

- High speed linear circuits

- High voltage switching arrays

- Opto-coupled photovoltaic devices

- Radiation resistant integrated circuits

Dielectric Isolation technology allows the fabrication of these product families because each active device area may be isolated in an individual tub region, separated from the other devices in the circuit. This eliminates parasitics that degrade circuit performance and improves reliability under conditions of extreme levels of ionizing radiation.

Sipex is actively involved in advanced processing techniques related to cost reduction of the material and improved island thickness control. In addition, research is currently underway to provide material's processing that may be applied to very high speed CMOS and BIMOS technologies.

In addition, Sipex provides services related to the deposition of polycrystalline silicon, wafer thinning and chemical etching for transducer and solar cell applications.

# MILITARY PROGRAM PARTICIPATION

Sipex Corporation plays a vital part and is an expert in many major military and space programs, both in the United States and Europe. Some of the programs Sipex Corporation participates in are:

| <del></del>       |                   |

|-------------------|-------------------|

| • SPACE SHUTTLE   | • SPACE LAB       |

| • F-15            | • TORNADO         |

| • F-16            | • STING RAY       |

| • F-18            | • JAS 38          |

| • STD MISSILE     | • ALRM            |

| • F-111           | • SPEARFISH       |

| • B-1             | • HOT             |

| • SEA SPARROW     | • DM2A3 TORPEDO   |

| • TOW-2           | • ROLAND          |

| MAVERICK          | • LEOPARD I & II  |

| • MILSTAR         | • AIRBUS 310      |

| ● EA6B/B-1        | • MAGIC           |

| • SPARROW MISSILE | • MIRAGE 2000     |

| • PIVADS          | • HARM MISSILE    |

| • MIRAGE F1       | • LARZAC & CFM 56 |

| • AMRAAM          | • TRIDENT         |

|                   | • SICBM           |

|                   |                   |

# SALES, SHIPPING & SERVICE INFORMATION

#### **ORDERING INFORMATION**

Orders may be placed with either our regional sales offices, sales representatives or directly with sales headquarters. Addresses and telephone/FAX numbers are listed in the sales office directory.

International: Customers outside the United States are served by Sipex's subsidiaries; Sipex Systems GmbH and Sipex Systems U.K. Ltd; Sipex Systems S.A.R.L.; or international sales representatives located throughout Europe, the Far East, and Canada. All international orders may be placed with either our international sales offices, sales representatives or directly with International Sales Department at sales headquarters. Addresses and telephone/FAX numbers are listed in the sales office directory.

#### **TERMS AND CONDITIONS OF SALE**

Price and delivery information of any item in this catalog is available from our sales representatives or direct from the Company. Quotations are F.O.B. factory of origin, and are subject to change without notice. On all orders, payment is net 30 days following date of shipment.

#### **APPLICATIONS ENGINEERING**

Sipex maintains a support staff of technical sales engineers, both domestically and internationally, who are expert in specific areas of analog, digital, and microelectronics technology. Staff engineers provide further technical support, as needed, on advanced circuit designs or application problems.

#### SHIPPING INSTRUMENTS

Shipping will be via United Parcel Service or Parcel Post unless other instructions are indicated. For rush service, we will ship by Air Freight, Air Express or Air Parcel Post on request.

#### WARRANTY

Sipex warrants its products to be free from defects in material and workmanship for a period of one year from the date of shipment. This warranty shall not apply to any product which has been abused or misused physically or electrically or whose leads have been clipped or soldered. Sipex's sole liability and the Purchaser's sole remedy under this warranty is limited to repairing or replacing defective components. Sipex shall not be liable for consequential damages under any circumstances.

#### **RETURNS**

When returning material for repair or replacement, it is necessary first to contact Customer Service. Upon acceptance of the request, a return material authorization will be issued. We require a detailed description of the reason for the return; the date and purchase order number on which it was obtained, and the date of receipt.

#### **SPECIFICATIONS**

Sipex reserves the right to discontinue items and change specifications without notice.

# NORTH AMERICAN SALES OFFICES/ SALES REPRESENTATIVES

# **REGIONAL SALES OFFICES:**

#### **EAST REGION**

Six Fortune Drive Billerica, MA 01821 Tel: (508) 663-7811 FAX: (508) 670-9001

#### **CENTRAL REGION**

102 South Tejon Street Suite 110 Colorado Springs, CO 80903 Tel: (719) 578-3346 FAX: (719) 578-8869

#### WESTERN REGION

491 Fairview Way Milpitas, CA 95035 Tel: (408) 945-9080 FAX: (408) 946-6191

#### SOUTHEAST REGION

10480 Little Patuxent Parkway Suite 500 Columbia, MD 21044 Tel: (301) 740-5676 FAX: (301) 740-5603

#### **ALABAMA**

SACS Norcross, GA 404-447-6154

# **ARIZONA**

SOUTHWEST TECH Phoenix 602-893-1209

## **ARKANSAS**

MREP Dallas, TX 214-484-5711

## **CALIFORNIA** (North)

H-TECH SALES I San Jose 408-453-2111

### **CALIFORNIA** (South)

H-TECH SALES II Laguna Hills 714-583-1488

#### CANADA (Que.)

ESP St. Laurent 514-737-9344

#### CANADA (Ont.)

ESP Mississauga 416-626-8221 Ottawa 613-236-1221

#### CANADA (Ont.)

ESP Ottawa 613-236-1221

#### CANADA (B.C.)

ESP Delta 604-943-0183

#### **COLORADO**

HOWARD ASSOC. Parker 303-841-5755

#### CONNECTICUT

SIPEX CORP. Billerica, MA 508-671-1940

#### **DELAWARE**

TECH SALES ASSOC. Willow Grove, PA 215-784-0170

#### **FLORIDA**

ELECTRO-CRAFT, INC. Clearwater 813-573-2277 Boca Raton 407-394-9686

#### **GEORGIA**

SACS Norcross 404-447-6154

#### **IDAHO**

OLSON TECH SALES Bellevue, WA 206-883-7792

#### ILLINOIS (North)

MARTAN, INC. Schaumburg 708-303-5660

#### **ILLINOIS (South)**

MIDWEST TECH SALES Lenexa, KS 913-888-5100

#### **INDIANA**

STB ASSOC. Indianapolis 317-844-9227

#### **IOWA**

MIDWEST TECH SALES Cedar Rapids 319-393-5115

#### **KANSAS**

MIDWEST TECH SALES Goddard 316-794-8565

#### **KENTUCKY**

STB ASSOCIATES Louisville 502-499-6404

#### LOUISIANNA

MREP Dallas, TX 214-484-5711

#### MAINE

SIPEX CORP. Billerica, MA 508-671-1940

## MARYLAND

EES Annapolis 301-269-6573

#### **MASSACHUSETTS**

SIPEX CORP. Billerica, MA 508-671-1940

#### **MICHIGAN**

TRITECH SALES Farmington Hills 313-553-3370

#### **MINNESOTA**

WILLMAN ASSOC. Brooklyn Ctr 612-566-5010

#### MISSISSIPPI

SACS Norcross, GA 404-447-6154

#### **MISSOURI**

MIDWEST TECH SALES Earth City 314-298-8787

#### **MONTANA**

HOWARD ASSOC. Parker, CO 303-841-5755

#### **NEBRASKA**

MIDWEST TECH SALES Lenexa, KS 913-888-5100

### **NEVADA**

SIPEX CORP. Milpitas, CA 408-945-9080

### **NEW HAMPSHIRE**

SIPEX CORP. Billerica, MA 508-671-1940

#### **NEW JERSEY (North)**

PHASE 4 Fairfield, NJ 201-575-4343

#### **NEW JERSEY (South)**

TECH SALES ASSOC. Willow Grove, PA 215-784-0170

#### **NEW MEXICO**

SOUTHWEST TECH Phoenix, AZ 602-893-1209

#### **NEW YORK (Metro)**

PHASE 4 Great Neck, NY 516-482-1790

#### **NEW YORK (Up-State)**

MICRO-TECH MKTG. Rochester 716-328-3000 Kingston 914-338-7588 N. Syracuse 315-458-5254

#### **NORTH CAROLINA**

SACS Raleigh 919-859-9970

#### **NORTH DAKOTA**

WILLMAN ASSOC. Brooklyn Ctr, MN 612-566-5010

#### OHIO

J.N. BAILEY & ASSOC. New Lebanon 513-687-1325 Columbus 614-262-7274 Brunswick 216-273-3798

## **OKLAHOMA**

MREP Dallas, TX 214-484-5711

#### **OREGON**

OLSON TECH SALES Beaverton, OR 503-643-9488

#### **PENNSYLVANIA (East)**

TECH SALES ASSOC. Willow Grove 215-784-0170

### PENNSYLVANIA (West)

J.N. BAILEY & ASSOC. Columbus, OH 614-262-7274 Brunswick, OH 216-273-3798

### **RHODE ISLAND**

SIPEX CORP. Billerica, MA 508-671-1940

## **SOUTH CAROLINA**

SACS Raleigh, NC 919-859-9970

#### **SOUTH DAKOTA**

WILLMAN ASSOC Brooklyn Ctr., MN 612-566-5010

#### **TENNESSEE**

SACS Norcross, GA 404-447-6154

#### **TEXAS**

MREP Dallas 214-484-5711 Houston 713-988-7613

#### **UTAH**

HOWARD ASSOC. Parker, CO 303-841-5755

#### **VERMONT**

SIPEX CORP. Billerica, MA 508-671-1940

#### **VIRGINIA**

EES Annapolis, MD 301-269-6573

#### WASHINGTON

OLSON TECH SALES Bellevue 206-883-7792

#### WASHINGTON, D.C.

EES Annapolis, MD 301-269-6573

## **WEST VIRGINIA**

SIPEX CORP. Columbia, MD 301-740-5676

#### **WISCONSIN**

LARSEN Wauwatosa 414-258-0529

#### WYOMING

HOWARD ASSOC. Parker, CO 303-841-5755

# NORTH AMERICAN AUTHORIZED DISTRIBUTORS

#### **CALIFORNIA**

JAN DEVICES, INC. Reseda, CA 818-708-1100

MILGRAY Camarillo, CA 805-484-4055

#### CONNECTICUT

MILGRAY Milford, CT 203-878-5538 800-922-6911

#### **FLORIDA**

MILGRAY Winter Park, FL 407-647-5747 800-432-0645

#### **GEORGIA**

MILGRAY Norcross, GA 404-446-9777 800-241-5523

#### **ILLINOIS**

MILGRAY Arlington Heights, IL 312-253-1212 800-322-6271

## **KANSAS**

MILGRAY Overland Park, KS 913-236-8800

#### **MASSACHUSETTS**

MILGRAY Wilmington, MA 508-657-5900

NORTHSTAR ELECTRONICS Wilmington, MA 508-657-5155

#### **MARYLAND**

MILGRAY Columbia, MD 301-621-8169 800-638-6656

#### **MICHIGAN**

CALDER ELECTRONICS Grand Rapids, MI 616-698-7400

#### **NORTH CAROLINA**

MILGRAY Raleigh, NC 919-790-8094 800-562-3118

#### **NEW JERSEY**

MILGRAY Marlton, NJ 609-983-8010 800-257-7111

MILGRAY Parsippany, NJ 201-335-1766

#### **NEW YORK**

MILGRAY Farmingdale, NY 516-391-3000 800-MILGRAY

### **NEW YORK**

MILGRAY Pittsford, NY 716-381-9700

#### OHIO

MILGRAY Cleveland, OH 216-447-1520 800-321-0006

#### **TEXAS**

MILGRAY Dallas, TX 214-248-1603 800-637-7227

MILGRAY Stafford, TX 713-240-5360

OMNI PRO ELEC Dallas, TX 214-233-0500 800-356-9095

#### UTAH

MILGRAY Salt Lake City, UT 801-272-4999

#### **WISCONSIN**

MARSH ELECTRONICS Milwaukee, WI 414-727-6000

#### CANADA

MILGRAY Willowdale, Ontario 416-756-4481 800-268-3315

# INTERNATIONAL SALES OFFICES

#### **GERMANY**

#### SIPEX GmbH

Rheinstrasse 32 6100 Darmstadt West Germany Tel: 06151-291595 Fax: 06151-292762

#### SIPEX GmbH

Moosstrasse 10 A 8130 Starnberg West Germany Tel: 08151-89810 Fax: 08151-7598

#### SIPEX GmbH

Wacholderstrasse 38 2000 Wedel/Holstein West Germany Tel: 04103-2845 Fax: 04103-7534

#### FRANCE

#### SIPEX S.A.R.L.

14, Rue du Morvan SILIC 525 94633 Rungis Cedex France

Tel: 01-46-87-83-36 Fax: 01-45600784

#### **ENGLAND**

#### SIPEX LTD

333 London Road Camberley Surrey GU15-3HQ England

Tel: 0276-28128 Fax: 0276-691131

#### **JAPAN**

#### NIPPON SIPEX CORP.

Tohyama Building 81 Yamabuki-chyo Shinjuku-ku Tokyo 162 Japan

Tel: 03-266-8585 Fax: 03-266-8587

# **INTERNATIONAL SALES REPRESENTATIVES**

#### **AUSTRIA**

#### SIPEX GmbH

Rheinstrasse 32 6100 Darmstadt West Germany Tel: 06151-291595 Fax: 06151-292762

#### BELGIUM

#### BETEA SA/NV

Leuvensesteenweg 31 B-1940 Sint-Stevens-Woluwe Belgium

Tel: 027368050 Fax: 027251619

## **DENMARK**

## E. FRIIS MIKKELSEN A/S

Kroashoivei 51 DK-2880 Bagsvaerd Denmark Tel: 02-986333 Fax: 02-988140

#### **FINLAND**

#### OXXO OY AB

Latokartanontie 7A5 SF-00700 Helsinki Finland

#### **ISRAEL**

## SEG TEC

Office 10 Ashita Street Holon Israel

Tel: 972-3-5567458 Fax: 972-3-5569490

#### **ITALY**

#### CELTE S.R.L.

Via le Lombardia 15 20131 Milano Italy

Tel: 02-2367602 Fax: 02-2666960

### **KOREA**

#### SUNHO CORPORATION

Seoul Yeong Dong P.O. Box 1846 Seoul Tel: 02-558-4415

Fax: 02-558-4412

#### **NETHERLANDS**

#### **KONING EN HARTMAN**

P.O. Box 125 2600 AC Delft **Netherlands** Tel: 031-15-609906 Fax: 031-15-19194

#### **NORWAY**

# ESTRONIC A/S

Torstadbakken 4B P.O. Box 174 N-1364 Hvalstad Norway Tel: 02-846010 Fax: 02-981677

#### **SPAIN**

#### ANATRONIC S.A.

Avda de Valladolid, 27 E-28008 Madrid Spain

Tel: 034-1-542-4455 Fax: 034-1-248-6975

#### SWITZERLAND

#### ABALEC AG

Grabenstrasse 9 CH-8952 Schlieren Switzerland Tel: 041-1-730-0455

Fax: 041-1-730-9801

#### TAIWAN

#### KALTEC INT'L LTD

18, Lane 46, Sec. 2 Shuang Shi Road Panchiao City Taipei, Taiwan R.O.C. Tel: 2-2537387

Fax: 2-2537636

# APPLICATION NOTES

# APPLICATION NOTE SELECTOR GUIDE

| PA                                               | GE   |

|--------------------------------------------------|------|

| Digitizing Dynamic Signals                       | 3    |

| Quad S/H Solves Acquisition Problems             | . 11 |

| CMOS DACs Important Considerations Above 12-Bits | . 17 |

| Analog Processing for Data Acquisition           | 27   |

# DIGITIZING DYNAMIC SIGNALS

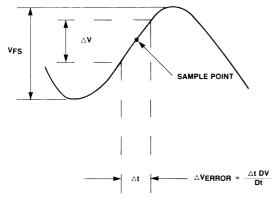

When using Analog/Digital Converters based on the successive approximation technique, careful attention must be paid to the dynamic behavior of the circuit in order to achieve the desired accuracy. This article shows how the desired accuracy can be maintained with rapidly changing dynamic signals.

### INTRODUCTION

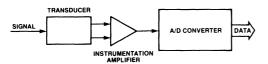

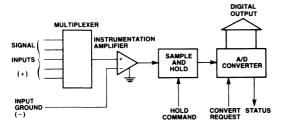

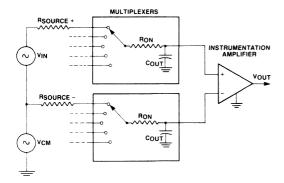

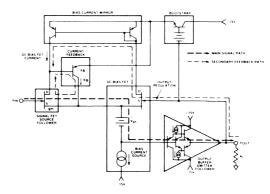

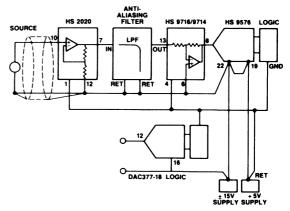

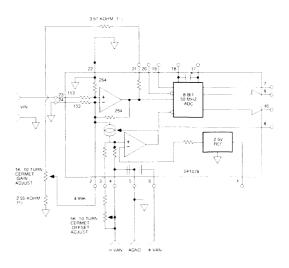

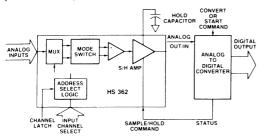

The block diagram in Figure 1 shows the typical configuration of a data acquisition system used to convert an analog value into a corresponding binary form. The analog signal, which is often non-electrical in nature (like pressure, temperature, pH-value, distance) is converted to an electrical voltage by a sensor or transducer. In many cases, this voltage has an amplitude of just a few millivolts and is often superimposed on a common mode voltage. The instrumentation amplifier suppresses the common mode voltage and amplifies the analog signal to a level which is useful for subsequent processing (e.g., 0 to + 10 volts). Additional function blocks like low pass- or anti-aliasing-filters (to suppress noise and unwanted frequency bands) can be inserted between the instrumentation amplifier and the A/D Converter. After the conversion has been completed, the ADC will output a digital word which corresponds to the value of the analog input signal Depending on the desired function of the circuit, the digital word can be further processed by a computer or microprocessor

To test the performance of such a circuit (as shown in Figure 1), usually a variable voltage source is used as the input instead of the sensor or transducer. Provided that the instrumentation amplifier has a linear transfer function and the ADC meets its specifications (especially differential linearity), all possible bit combinations (e.g., 4096 for 12-bit resolution) can be produced at the output of the ADC by varying the input voltage source. But once a dynamically changing voltage source, like a function generator, is connected to the analog input to simulate the response of the transducer, substantial linearity errors and so-called "missing codes" can be observed. This can easily degrade the accuracy of the data acquisition system from 12 to 10 or 8 bits or less. The reasons for this performance degradation and how these errors can be eliminated will be described below.

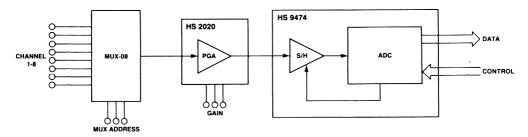

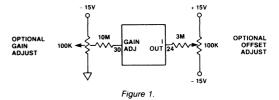

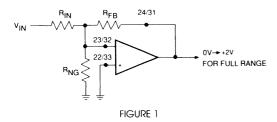

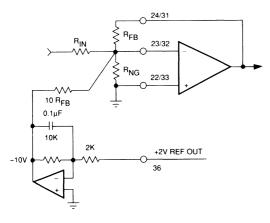

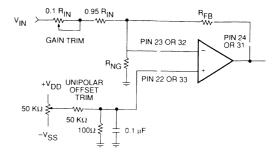

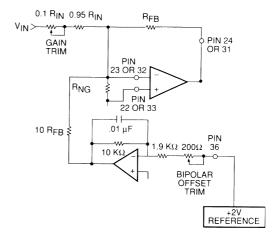

Figure 1. Block Diagram of a Data Acquisition System

# **CONVERSION PRINCIPLES**

Several analog-to-digital conversion techniques have been developed which are tailored to the specific needs of different applications. Following is a short description of the three major techniques.

Integrating A/D Converters: Integrating or Dual-Slope ADCs were the first on the market. They consist of a charging capacitor, a current source, an analog comparator and a digital counter with clock. The conversion is done in two phases. During the first phase, the capacitor is charged with a current derived from the input voilage for a fixed amount of time. In the second phase, the counter is started and the capacitor is discharged with a constant current source. The comparator stops the counter as soon as the capacitor is completely discharged. The reading of the counter is directly proportional to the value of the input signal. The conversion of the input signal and the conversion time is directly dependent on the value of the input signal.

Integrating ADCs offer medium to high resolution at conversion speeds of 1 to 1000 samples per second. Their characteristics include high noise immunity, relatively simple design and low cost. Applications include digital voltmeters and acquisition of slow changing signals such as temperature. Special conversion techniques like Quad-Slope have been derived from the Dual-Slope principle for special applications such as very high precision voltmeters.

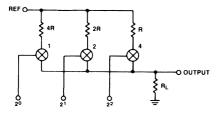

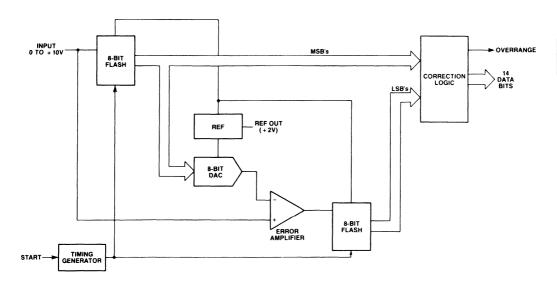

Flash A/D Converters: Offering the highest possible speed, Flash-converters are used in applications such as waveform recording and digitizing video signals. Sampling rates exceeding 100 MHz are no longer a talk of the future. This extremely high conversion speed is achieved with a single-step architecture. A reference voltage is applied to the top of a ladder of resistors with equal value. Each tab of the ladder is connected to one input of a voltage comparator, while the other input of each comparator is connected to the input voltage. For N bits of resolution, 2N-1 resistors and comparators are required. This limits the resolution of currently available Flash-converters to 10 bits (requiring 1023 resistors and comparators). Each comparator compares the input voltage with the scaled reference voltage resulting in a "bar"-type output code. A digital encoder finally converts the linear "bar"-type code into a binary code

Successive Approximation (SAR-type) A/D Converters: This type of ADC fills the gap between the high resolution/low speed integrating ADC and the extremely fast, low resolution Flash converter. SAR-type ADCs offer medium to high resolution with conversion speeds of 10,000 to 1,000,000 samples per second.

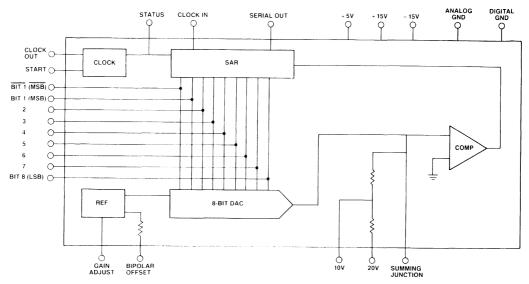

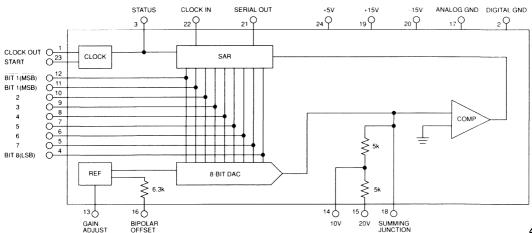

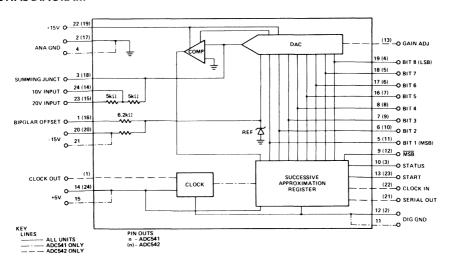

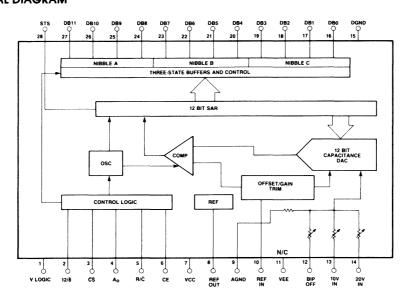

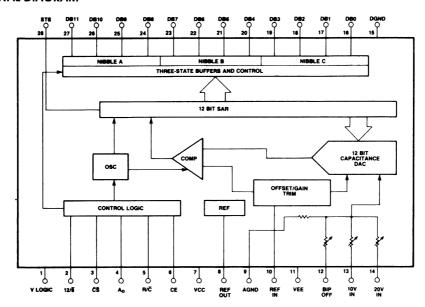

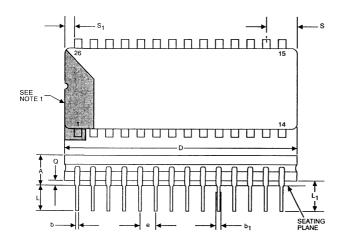

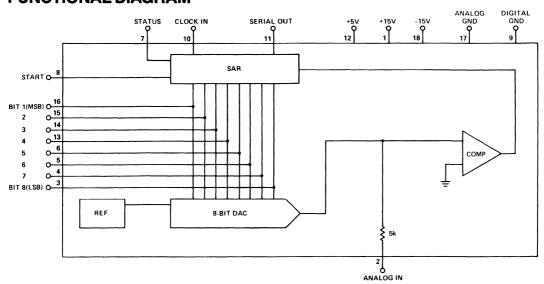

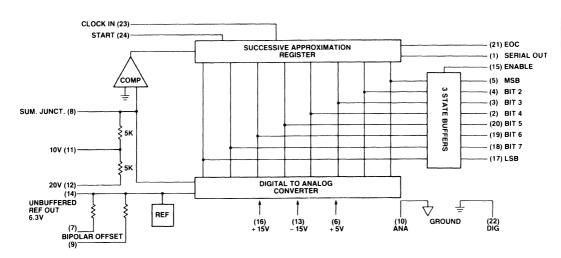

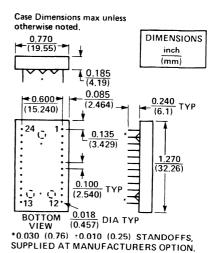

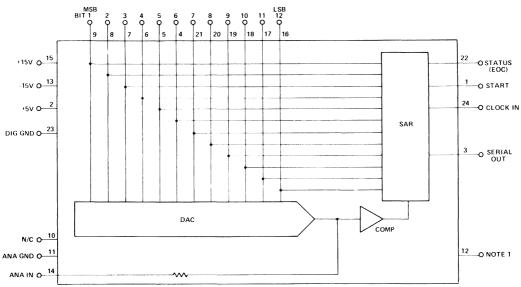

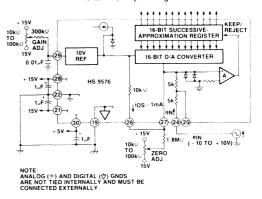

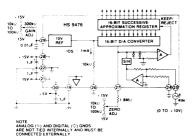

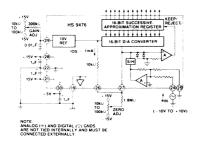

Figure 2. Functional Diagram of an A/D Converter with SAR

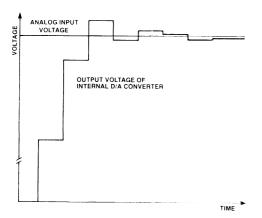

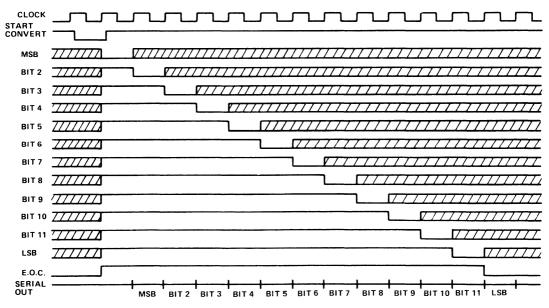

Figure 3. Internal Sequence of an A/D Conversion

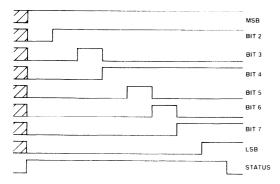

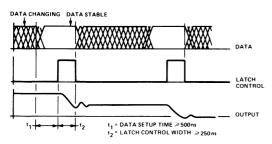

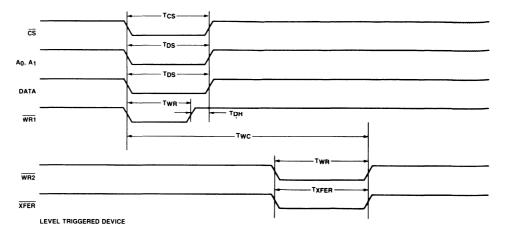

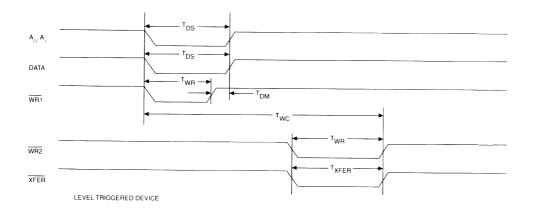

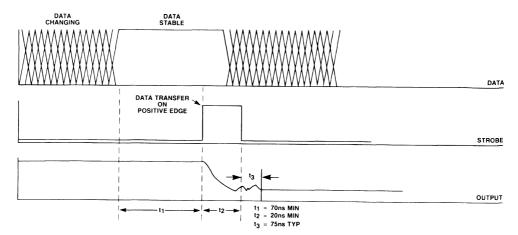

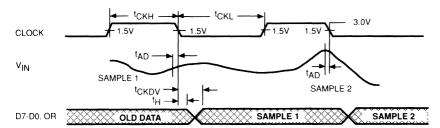

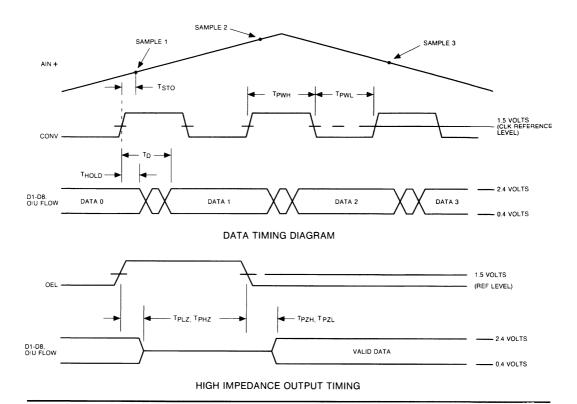

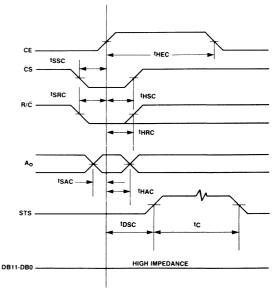

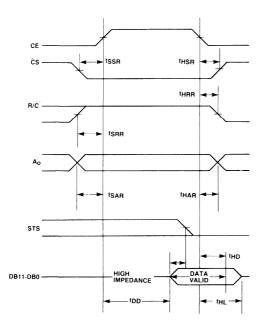

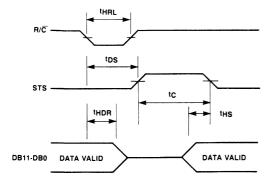

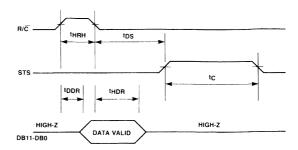

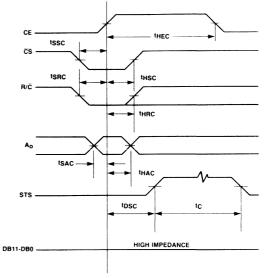

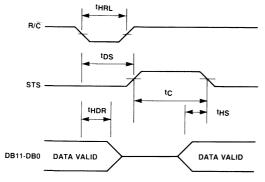

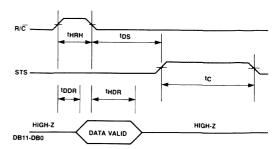

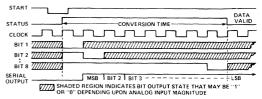

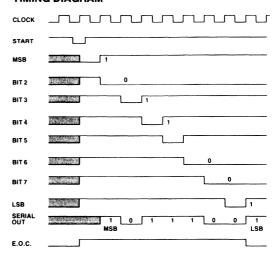

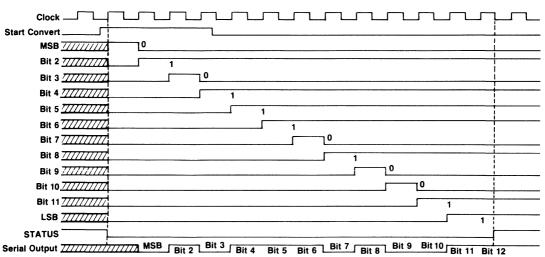

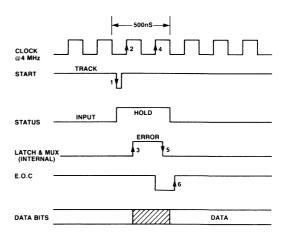

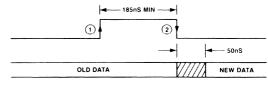

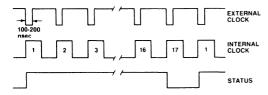

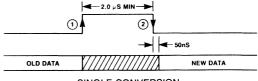

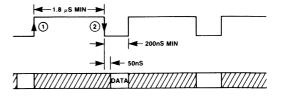

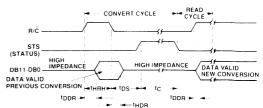

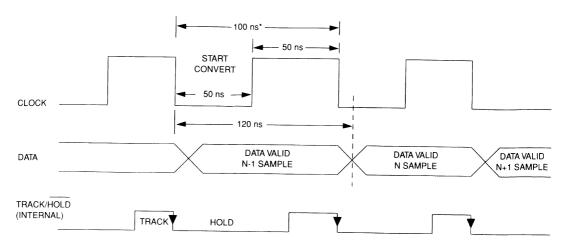

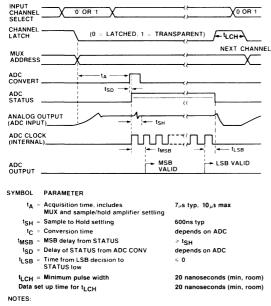

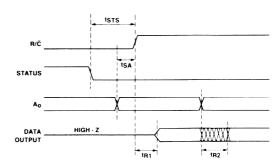

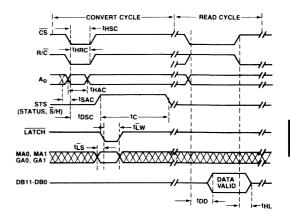

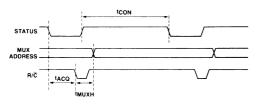

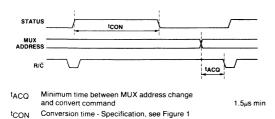

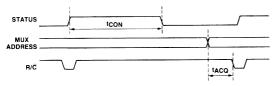

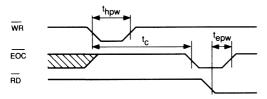

Figure 4. Timing Diagram

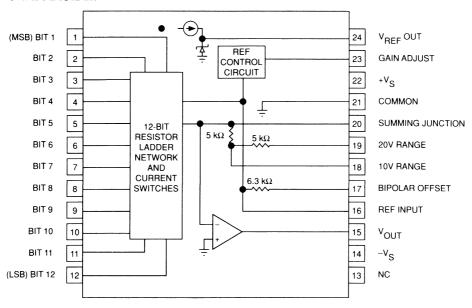

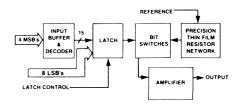

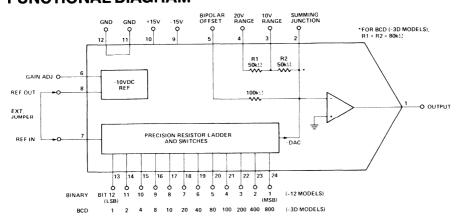

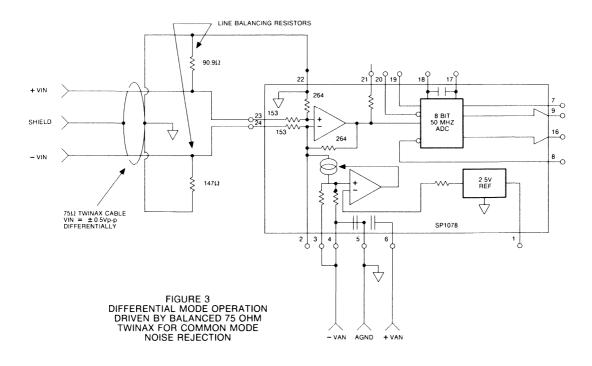

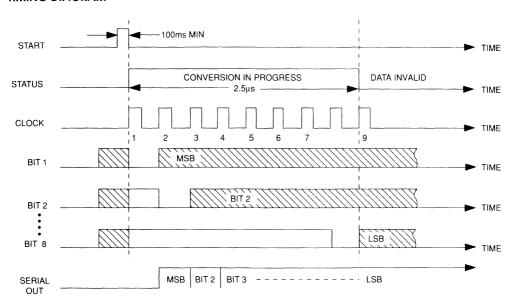

Figure 2 shows a block diagram of an 8-bit SAR-type ADC. The main building block is a Digital/Analog-Converter which determines the accuracy of the ADC. A comparator compares the output of the DAC with the analog input and provides a digital signal to the "Successive Approximation Register" (SAR). During the conversion time the SAR generates a digital code in such a manner that the output of the DAC equals the analog input signal. For N bits of resolution only N clock cycles are required, far less than that for the integrating converter. Some converters require one additional clock pulse at the beginning of the conversion cycle to reset the SAR. The SAR determines the digital code in the same way as an unknown weight is determined with a beam balance with the least number of decisions.

At the beginning of a conversion cycle, the MSB (Most Significant Bit) is switched on with all other bits switched off. After the output of the DAC has settled, the comparator decides whether the output voltage is greater or smaller than the input voltage and provides this information to the SAR. If the DAC output is smaller than the input voltage, the MSB remains switched on; otherwise it is reset to zero. The MSB of the final digital output is valid after the first clock cycle and may be read out (this is normally done for serial output). With the next clock pulse the second bit is switched on and based on the comparator's decision, is reset to zero or remains set. This process is repeated until the SAR has switched on all the remaining bits and latched the comparator's decisions. The sequence over time of the A/D conversion is shown in Figure 3. It can be clearly seen how the DAC's output voltage approaches the input signal during the conversion cycle. Figure 4 shows the corresponding timing diagram.

# PERFORMANCE DEGRADATION

It is essential to monitor the effects of changes in the input signal during an analog-to-digital conversion for the different conversion techniques. The output code of an integrating ADC depends on the amount of charing current applied to the capacitor during the first phase of the conversion. A change in the input signal during the second phase will not affect the result. Flash converters take an instantaneous snapshot of the input signal, so the input signal doesn't really change during conversion. However, it must be determined at which point during the conversion time the data is latched from the comparator outputs into the digital encoder.

For SAR-type ADCs the output code may represent any of the voltages between the start and the end of the conversion. Therefore, it is extremely important to keep the input voltage constant once a conversion has been started. The following example shows why. At the beginning of a conversion the input voltage may be just a little bit higher than the value of the MSB. After the first clock cycle the MSB will remain set. If the input voltage decreases during conversion to a value lower than the MSB, the resulting code will be erroneous because the MSB remains switched on. Once a comparator has made a decision it cannot subsequently be changed. However, the successive approximation principle, by its nature, insures that the digital code approximates the actual value, so errors are corrected within a limited band. For that reason the remaining error will never be greater than the voltage change during a conversion and no totally erroneous codes will be generated. At least the magnitude of the error can be estimated that way

When digitizing an analog waveform, the samples must be taken at precisely determined sampling intervals in order to be able to reconstruct the original signal. Even though some kind of error correction takes place during the conversion time, it cannot be said whether the digital code represents the input signal at the beginning or the end of the conversion time or somewhere in between.

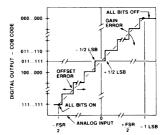

When the analog input signal changes during the conversion time, not only will the output code be erroneous, but some of the codes might also disappear. Since these codes can't be produced with any input voltage, this reduces the effective resolution of the A/D Converter. It doesn't make economical sense to use a 12-bit ADC when only 10 or 8 bits of effective resolution are achieved. As a rule of thumb, the analog input signal should not change more than ½ LSB during the conversion time (which will produce a maximum linearity error of ½ LSB) to maintain specified performance. This is because an ADC with a specified integral linearity error of ½ LSB will not have any ''missing codes'' and the full resolution is available. If, however, the ADC itself has an integral linearity error of ½ LSB, each additional error, regardless how small it is, can lead to missing codes.

Figure 5a shows a computer program which can be used to simulate an ideal ADC when the input signal changes during conversion. The program reconstructs the function of an ADC by comparing the changing input signal with the output of the internal DAC and issuing a corresponding bit stream to the comparator. The program listing has been simplified for easier understanding and although it is written in HP 85 basic, it can run on any computer after adapting the print format (line 200).

In Figure 5b the appropriate printout of two program runs can be seen. Column 1 shows the number of the clock cycle (cycle 0 is start of conversion) while column 2 shows the actual input voltage. The voltage level here is expressed in LSBs for simplification, but can be converted to any other voltage level by multiplication with a constant factor. Column 3 shows the digital code which is applied to the DAC and therefore compared with the input voltage. The comparator's decision is shown in the next column while the last column shows the SAR output code after the decision. The printout in Figure 5b shows two 12-bit conversions with input voltages of 2047.66 and 2047.67 LSBs, respectively. In both cases, the input voltage changes at a rate of +4 LSBs per conversion. With an analog input of 2047.66 LSBs, the resulting code is 2047; if the input voltage is raised just 0.01 LSB at the beginning of the conversion, the resulting code is 2051. Thus, the three successive codes 2048, 2049 and 2050 cannot be generated if the input voltage changes at a rate of +4 LSBs during the conversion time. This means the effective resolution of the 12-bit converter has been reduced to 9 bits in this case

Figure 5A. Program Listing

| 111.7 | LOFIGN<br>TAL POLTAGE<br>GE CONVERS                                                                          | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                | P            | t ŧ                                                           |

|-------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------|---------------------------------------------------------------|

| 1.,   | <b>*</b> ±                                                                                                   | H7 +                                                                 | 4            | **                                                            |

|       | 204 6.7<br>2046 00<br>2046 74<br>2046 00<br>2046 00<br>2046 4.7<br>2046 6.7<br>2050 00<br>2050 67<br>2051 00 | 3072<br>2560<br>2304<br>2176<br>2112<br>2080<br>2064<br>2056<br>2055 | 010000000000 | .0449<br>2044<br>2044<br>2044<br>2044<br>2044<br>2044<br>2044 |

| 11    | 3051 34<br>3051 67                                                                                           | 2050<br>2051                                                         | ì            | 2050<br>2051                                                  |

| INI               | DECTIÓN<br>FIAL VOLTAGE<br>NGE-CONMERS | 12 i<br>204;<br>4 L: | 66          | L SE |

|-------------------|----------------------------------------|----------------------|-------------|------|

| <b>#</b> 1        | #2                                     | #3                   | <b>#</b> -3 | # 5  |

|                   | 2047 66                                | 0                    | ñ           | 9    |

| .0                | 3647 39                                | 2048                 | ä           | ă    |

| *1<br>2<br>3<br>4 | 2045 33                                | 1024                 | 1           | 1024 |

| - 3               | 3048 66                                | 1536                 | i           | 1536 |

| 4                 | 2049 99                                | 1792                 | ī           | 1798 |

| 5                 | 2049 33                                | 1926                 | 1           | 1909 |

| è                 | 3049 66                                | 1984                 | 1           | 1984 |

|                   | 2049 99                                | 2016                 | 1           | 2016 |

|                   | 2050 33                                | 2032                 | 1           | 2032 |

|                   | 2050 66                                | 2040                 | 1           | 2040 |

| . 0               | 2050 99                                | 2044                 | 1           | 2844 |

| 1.1               | 2051 33                                | 2046                 | 1           | 2046 |

|                   |                                        |                      |             |      |

Figure 5B. Printout

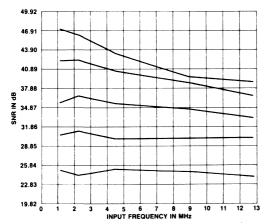

The corresponding input signal frequency can be easily calculated if the conversion time is known. For a popular ADC like the industry standard HS 574, which has a maximum conversion time of 30  $\mu$  sec. the corresponding input frequency would have been 16 Hz in this case — pretty low for a reduction from 12 to 9 bits in resolution.

Taking the above mentioned rule of thumb that the input signal should not change more than  $\frac{1}{2}$  LSB during conversion time, the following formula can be used to calculate the maximum input frequency.

$$f_{\text{max.}} = \frac{1}{2 \cdot \text{Pi} \cdot 2^{\text{N}} \cdot \text{conversion time}}$$

(1)

$(2^{N} = \text{number of codes}, e.g., 4096 for 12 bits of resolution})$

Using this formula, the maximum usable input frequency for the popular HS 574 is limited to 1.3 Hz (!), which is much too low for most applications and would make the high throughput rate of more than 30,000 samples per second unattainable (according to signal theory, two samples per period is sufficient to reconstruct the original signal...).

The above formula is based on the maximum slew rate of the input signal which for sine waves occurs during the zero crossing. Sometimes a slightly different formula (2) is applied which uses the average slew rate of a sine wave instead of the maximum slew rate. But even using this formula, the HS 574 would be limited to input frequencies of 2 Hz.

$$f_{\text{max.}} = \frac{1}{4 \cdot 2^{N} \cdot \text{conversion time}}$$

(2)

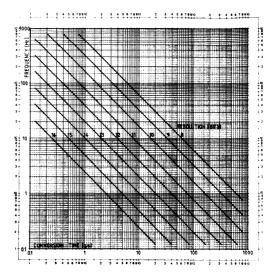

What are the implications to the user of this input signal limitation to 1.3 or 2.0 Hz? It simply means, that with input frequencies exceeding that limit, the specified accuracy of an A/D-Converter cannot be achieved. The appendix graphically shows the maximum input frequency as a function of conversion time and resolution for any given ADC.

## **TEST RESULTS**

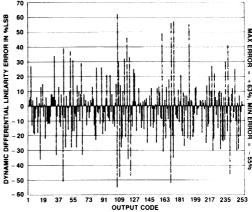

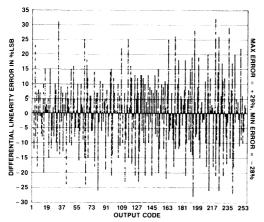

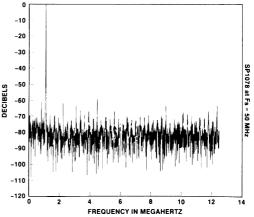

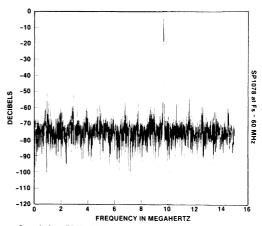

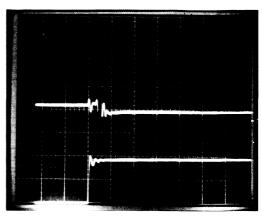

Because the quantitative measurement of the above mentioned errors is quite difficult, a special test set-up has been used to demonstrate the resulting effects and prove theory in practice. The experiment has been made with the HS 574 which is used for a wide range of industrial and military applications. The converter has been used in the 8-bit conversion mode which results in a conversion time of 15  $\mu$  sec. This has been done because the graphic resolution of the printer was limited to 256 dots (8 bits), but the results can be converted to any other resolution and conversion time.

The ADC has been selected for the smallest linearity error so that the results reflect the influence of the input signal slew rate instead of the ADC's linearity error. The sample used showed an integral linearity error of less than 0.1 LSB at 12-bit resolution which is about 5 times better than specified.

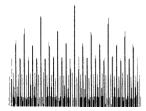

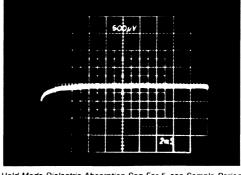

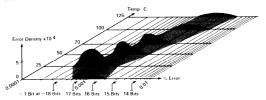

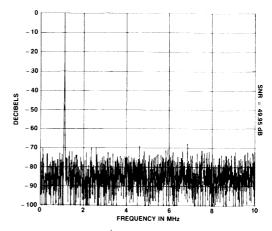

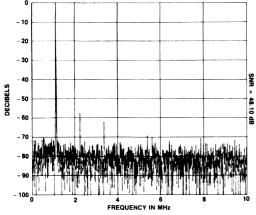

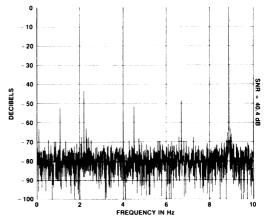

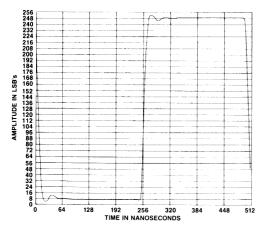

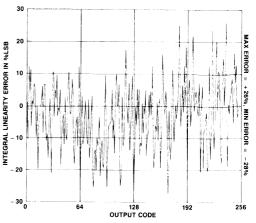

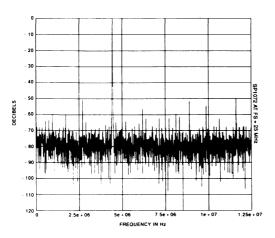

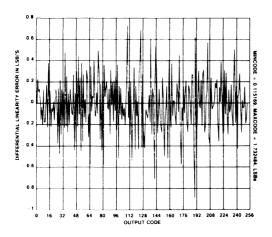

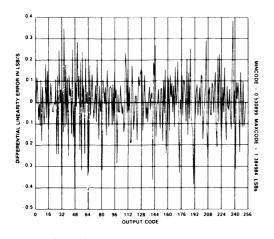

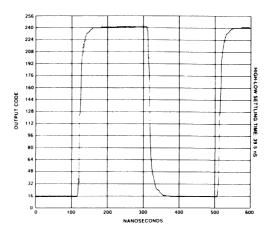

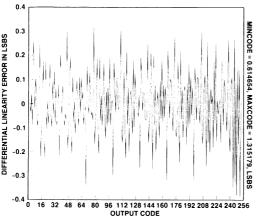

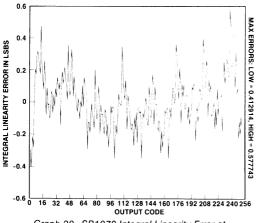

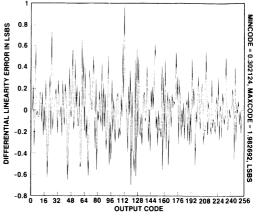

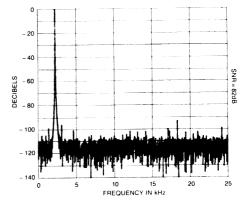

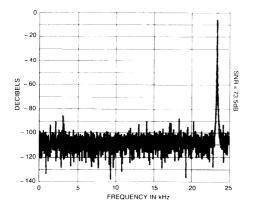

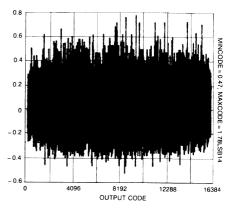

Figure 6A. HS 574 AK, 8-Bit Resolution, Signal Frequency 5000 Hz

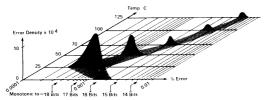

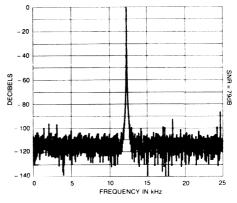

Figure 6B. HS 574AK, 8-Bit Resolution, Signal Frequency 1000 Hz

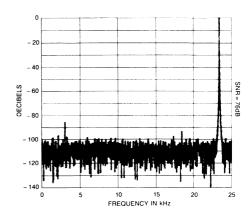

Figure 6C. HS 574AK, 8-Bit Resolution, Signal Frequency 41 Hz

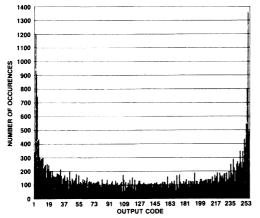

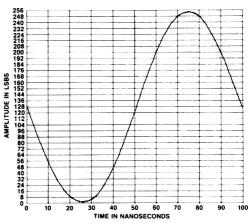

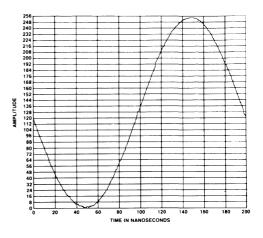

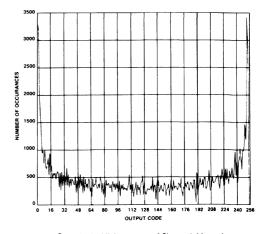

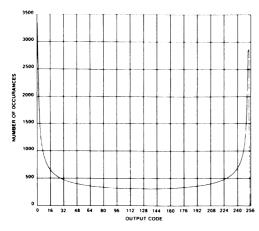

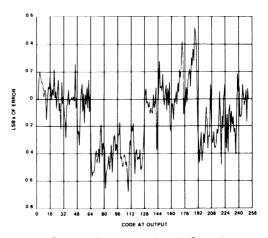

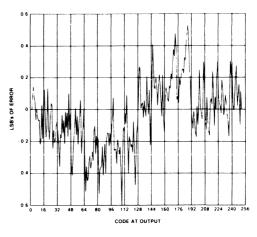

In the test set-up a triangular waveform (which means a signal with a constant slew rate) was applied to the analog input of the ADC. The signal frequency was 41 Hz which is just the maximum value for an 8-bit converter running at 15 sec per conversion. The sampling frequency of the ADC was chosen so that it was asynchronous with the input signal. The amplitude of the triangular wave was made slightly larger than the input voltage range of the ADC so that the reversing points did not fall into the transfer curve of the ADC.

A large number of samples of the input signal were then taken (about 100,000) and the digital data was fed to a desktop computer for statistical analysis. Figure 6 shows the results of measurements at three different frequencies. The x-axis is scaled from 1 to 254 which represents each output code while the y-axis shows the density of each output code, i.e., how often the particular code occurred during all measurements. With a perfectly linear ADC, you'd expect every possible output code to occur as often as any other code (roughly 400 times for 100,000 measurements at 8-bit resolution). In Figure 6a, which shows the result of the test with a frequency of 41 Hz, it can be seen that this is almost true — the density of the codes in the output spectrum is about the same for each code.

If one of the codes is a so-called "missing code," it will show a density of zero. This can be seen in Figure 6b, where the input frequency has been raised to 1000 Hz. Here more than 50 codes are missing while the remaining codes appear with many different densities. The two codes in the middle of the transfer function (127 and 128) appear more than 1500 times, almost 4 times more than they should. This shows that not only has the resolution been degraded, but the remaining codes exhibit large linearity errors as well. Keep in mind that the same kind of graph would show up at an input frequency of 62.5 Hz (1/16th of 1000 Hz) if the ADC's resolution were 12 bits. Figure 6c shows the results for a frequency of 5000 Hz (or 310 Hz for 12-bit resolution). Only 50 codes remained in the output spectrum while none of the other codes occurred even once during the 100,000 samples that were taken.

# HOW TO ELIMINATE THESE PROBLEMS

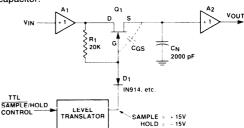

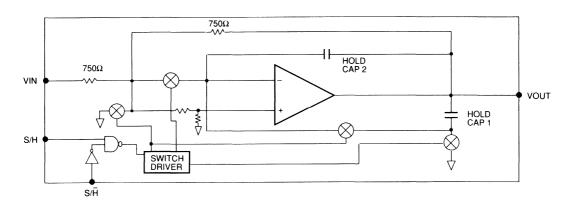

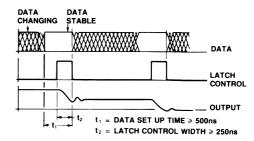

To obtain the full accuracy and resolution from your ADC, you must insure that the analog input signal does not change during the conversion time, i.e., the input signal must be frozen. This can be done with Sample/Hold (S/H) or Track/Hold (T/H) Amplifiers. (Both amplifier types are similar and can be used for that specific purpose, but only the expression Sample/Hold will be used hereafter.)

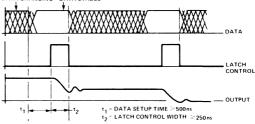

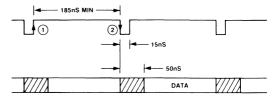

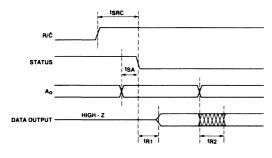

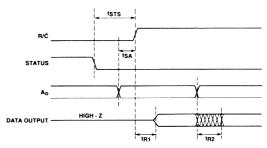

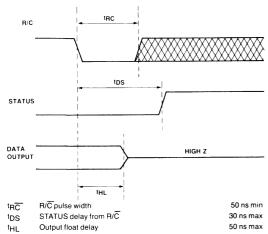

In most applications, the digital control input of the Sample/Hold can be driven directly from the STATUS- or EOC- (End of Conversion) line of the following A/D Converter. As long as no conversion is taking place, the Sample/Hold is in the sample mode and its output follows or tracks the input signal. In this mode the S/H functions just like an ordinary buffer amplifier with a gain of 1. As soon as a conversion has been started, this will be indicated by the STATUS-output of the ADC. This forces the S/H to switch from the sample mode to the hold mode, "freezing" the input voltage.

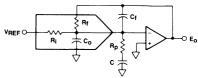

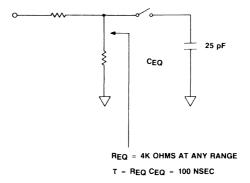

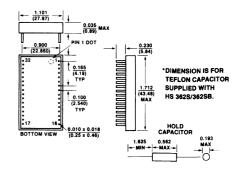

Sample/Hold amplifiers consist of three major building blocks: a capacitor, an analog switch and a buffer amplifier. In the sample mode the switch is closed and the input voltage appears across the capacitor. When entering the hold mode, the switch is opened and the previous input voltage is stored on the capacitor. The amplifier inside the S/H buffers the capacitor voltage and provides a low impedance output to the ADC. Some S/H amplifiers require an external hold

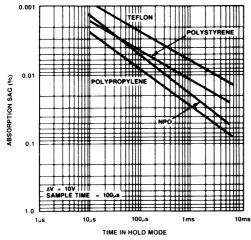

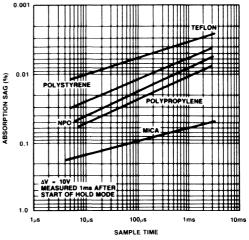

capacitor. This capacitor must be chosen very carefully, otherwise, it will memorize the previously stored voltage. This "memory" is caused by an effect called dielectric absorption. Therefore, only polystyrene or teflon capacitors are suitable for S/H applications because their dielectric absorption is fairly small.

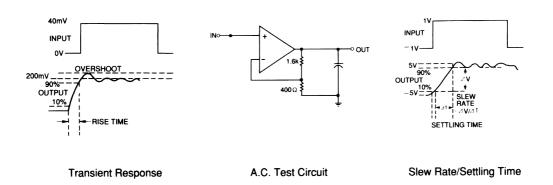

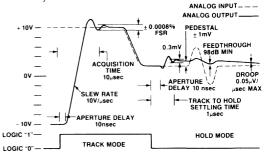

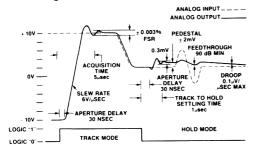

When selecting an S/H amplifier one could be confused with all the data sheet specifications. Below is a short description of the major S/H specifications.

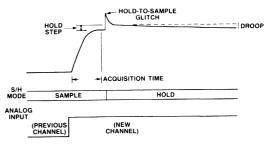

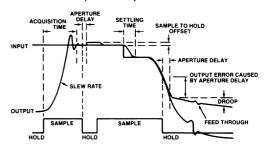

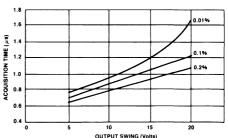

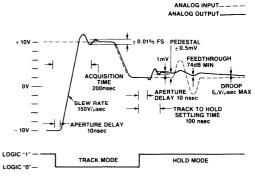

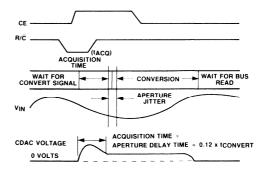

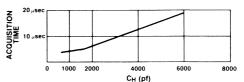

Acquisition Time: After switching from hold to sample mode, the S/H requires some time until the new input signal is acquired (the hold capacitor must be charged to the new voltage). The time which is required until the buffer output has settled within a certain error band to the new voltage is called acquisition time. After an analog-to-digital conversion has been completed, the next conversion cannot be initiated until the S/H has acquired a new input voltage. This delay is the S/H acquisition time.

Aperture Delay: The logic circuit inside the S/H requires some time to detect the S/H command and some time until the analog switch has fully opened. The sum of these times is the aperture delay. For high speed applications where it is important to have very precise timing, the S/H command can be advanced to compensate for this aperture delay.

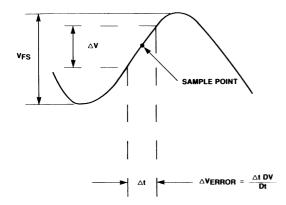

Aperture Uncertainty: This time is the variation of the aperture delay from one sample to the next one; it is sometimes called aperture jitter. This time is roughly 100 times less than the aperture delay and it determines the maximum usable input frequency for S/H amplifiers.\*

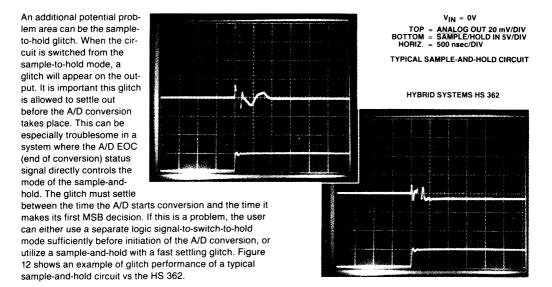

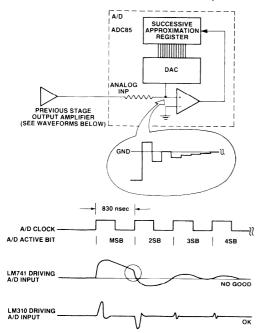

Hold Mode Settling Time: Every time the S/H switches from sample to hold, a glitch pulse can be seen at the output. The time required for the output to settle before the ADC's comparator makes the first (MSB) decision is the hold mode settling time.

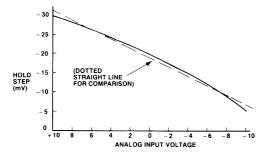

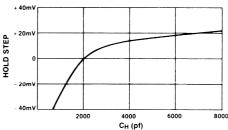

Sample-to-Hold Offset: This offset or pedestal is caused by a charge transfer of the analog switch when switching from Sample to Hold mode. As long as the resulting offset is linear with input voltage, it will be noticeable only as a small gain change and can be trimmed out easily.

**Droop Rate**: Due to leakage and bias currents the hold capacitor cannot hold the stored voltage indefinitely and therefore, it will discharge. This discharge is specified as Droop Rate and it must be kept in mind that Droop Rate normally doubles for every 10 °C rise in temperature.

The maximum frequency can be calculated with the formulas (1) and (2).

In the formulas conversion time has to be substituted with aperture jitter.

While the S/H eliminates many analog signal processing problems, it also has some drawbacks. Due to non-linearity of the Sample/Hold offset and other effects, the S/H will always add errors to the following ADC. If, for example, the S/H is specified for use in 12-bit linear systems, a S/H nonlinearity of 0.012% will be specified in the S/H data sheet, which equals ½ LSB at 12 bits. If you sum this error up with the ½ LSB linearity specification of the following ADC, the worst case linearity error will be 1 LSB which means that the **system accuracy** has been degraded to 11 bits. It also might be necessary to adjust the output offset of the S/H in addition to the offset adjustment of the ADC.

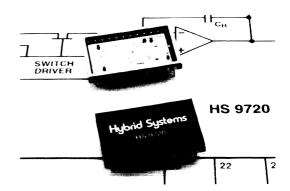

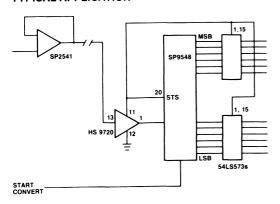

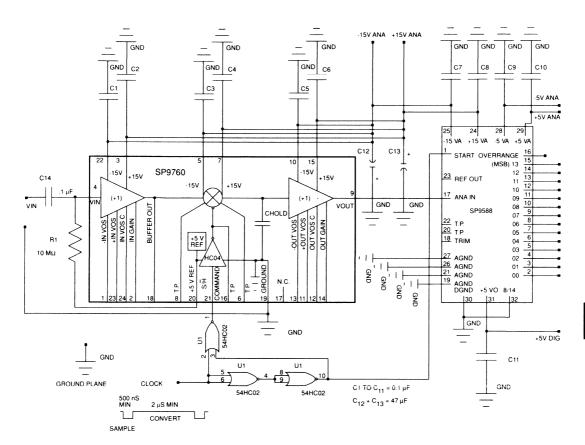

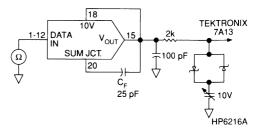

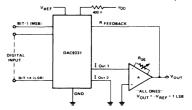

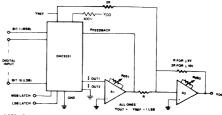

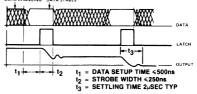

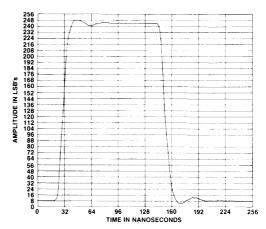

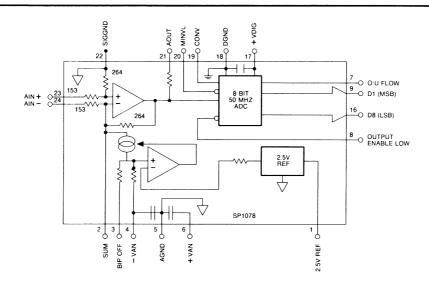

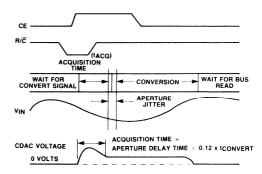

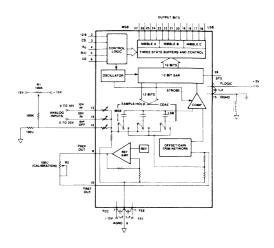

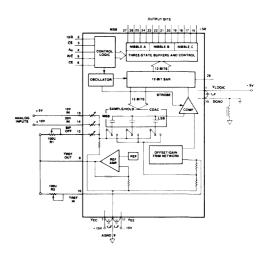

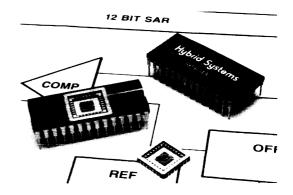

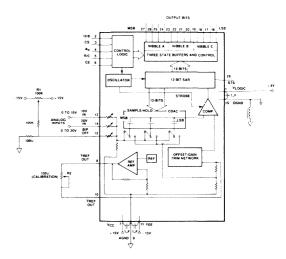

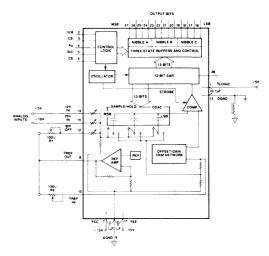

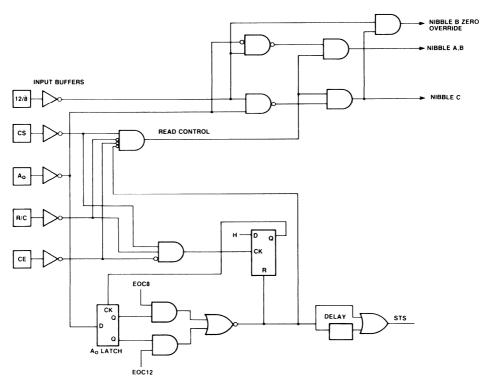

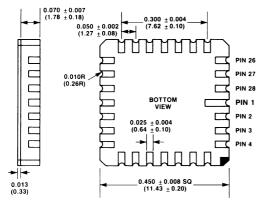

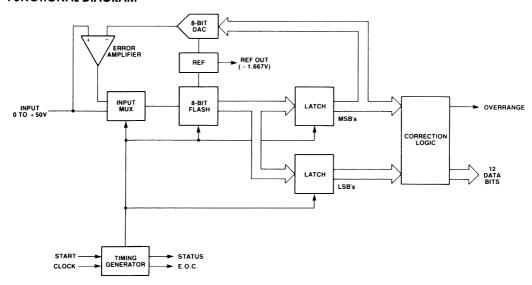

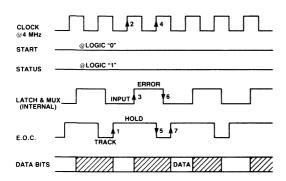

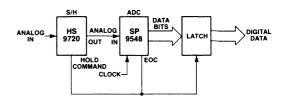

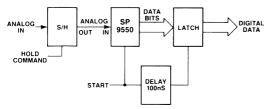

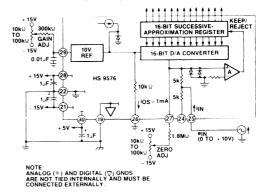

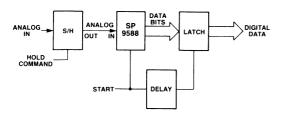

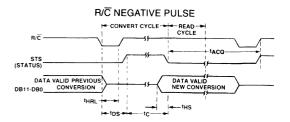

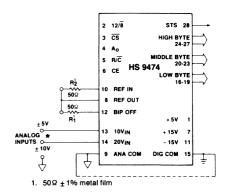

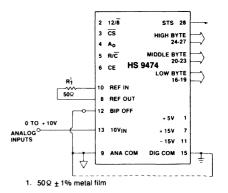

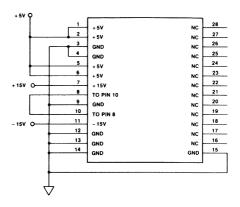

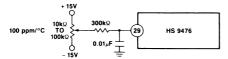

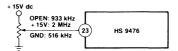

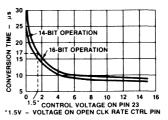

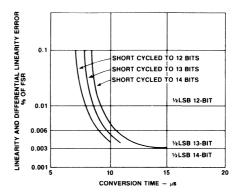

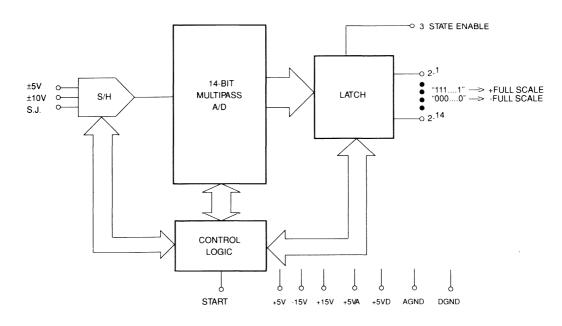

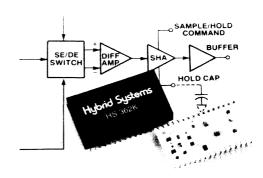

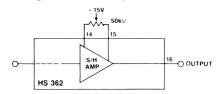

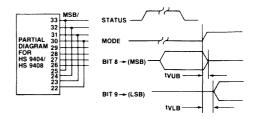

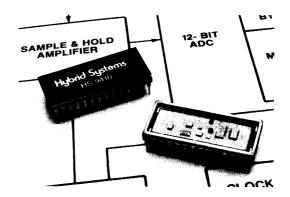

# SINGLE PACKAGE SOLUTION

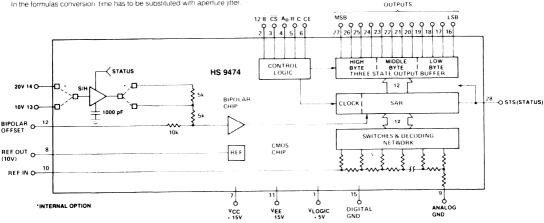

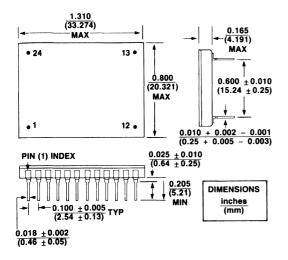

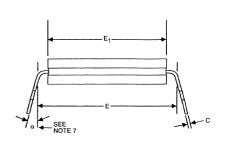

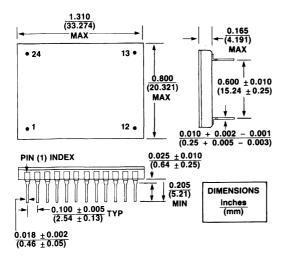

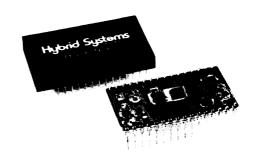

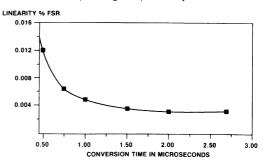

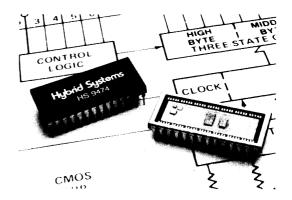

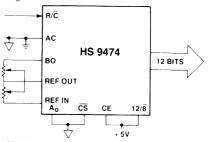

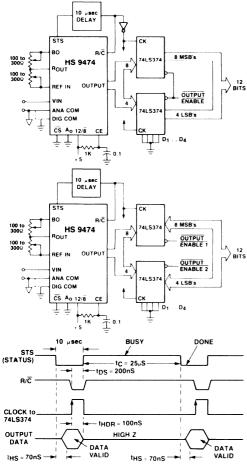

To overcome these disadvantages and still use the benefits of a S/H, Hybrid Systems has introduced the HS 9474, a 12-bit A/D Converter with built-in S/H amplifier. The ADC used in this device is the industry standard HS 574. All functions of the HS 574 such as microprocessor interface, software controlled 8- or 12-bit conversion and internal reference voltage are also available with the HS 9474. The Sample/ Hold command input of the S/H is directly connected to the STATUS output of the ADC so that the S/H is automatically in the hold mode during conversion and is switched back into the sample mode as soon as the conversion has been completed.

The specifications of the HS 9474, such as linearity, temperature drift and conversion time are identical to those of the HS 574 but with the S/H amplifier included. This means the errors of the S/H do not add to the errors of the ADC; they are included in the ADC specifications. The required hold capacitor is also included in the HS 9474, eliminating the need for external components and the possibility of errors due to dielectric absorption of the capacitor.

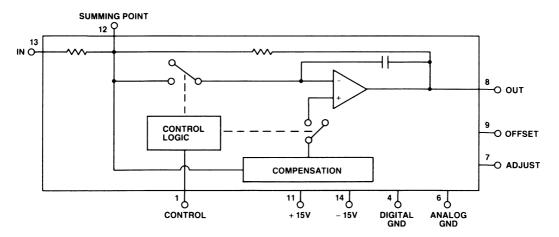

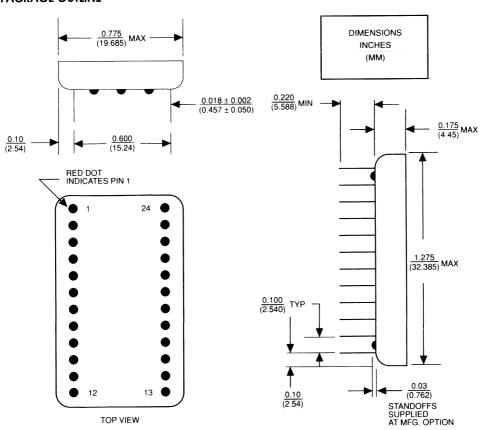

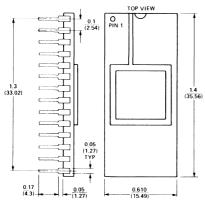

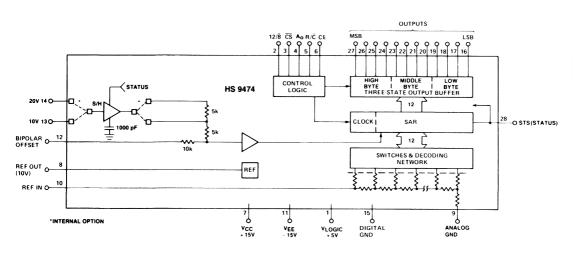

Figure 7 shows the block diagram of the HS 9474. It is important to notice that the HS 9474 is pur compatible with the HS 574. This allows existing designs which use a S/H amplifier to be upgraded to the HS 9474 without any hardware or software modifications. Also, universal A/D interfaces can be equipped with the HS 574 or HS 9474 depending on the application. In all existing designs where a 574 is used with an external S/H amplifier, the 574 and the S/H can be replaced by a HS 9474 when a connection is made from the input to the output pin of the S/H layout. This not only reduces the cost for stock and incoming inspection (one component instead of 2-4), but also improves system accuracy and even maintains compatibility to the existing design.

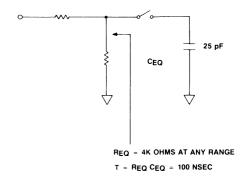

Figure 7. HS 9474 Functional Diagram

Attention must be paid to the acquisition time of the S/H amplifier. To acquire a new analog signal, a time span of 10  $\mu$  sec (max) is required between two consecutive conversions. Because the output data of the ADC must be read and stored in memory, this time span is available in almost any application. While the digital data is transferred, the S/H already acquires the new input signal. Unlike the HS 574, the input impedance of the HS 9474 is very high eliminating the need for additional buffer amplifiers. Due to the relatively low input impedance of the 574 (3 to 14k ohm), a buffer amplifier is required if the signal source doesn't have a very low output impedance.

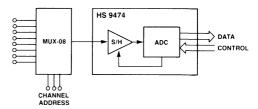

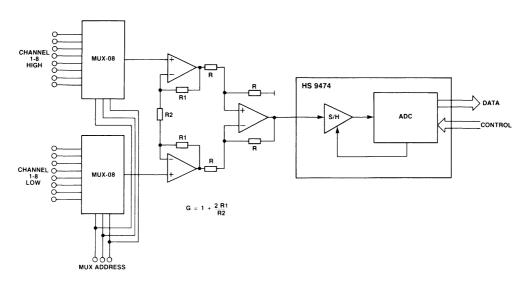

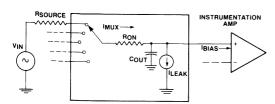

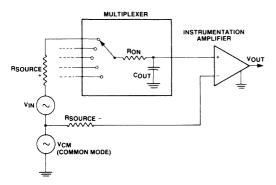

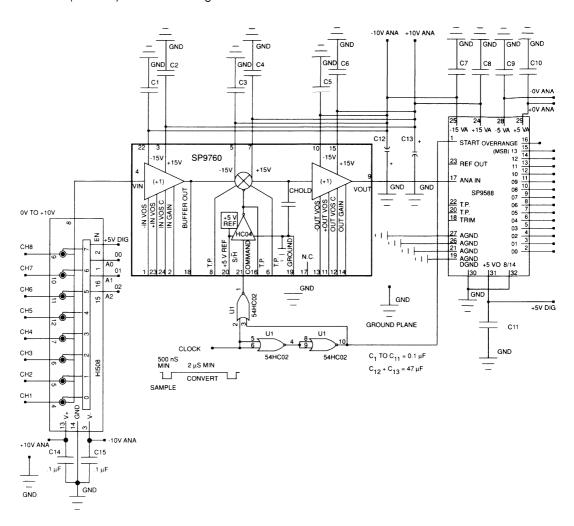

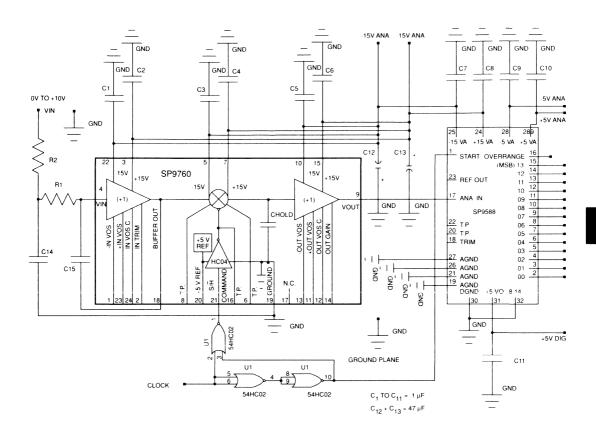

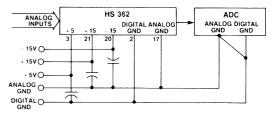

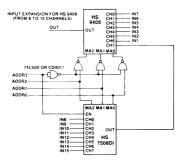

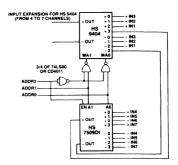

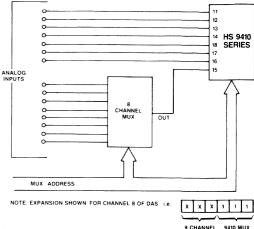

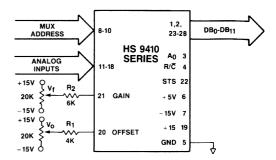

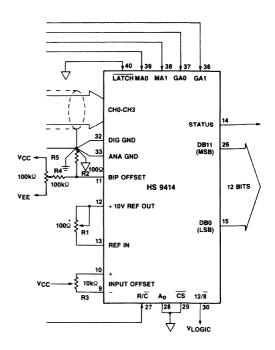

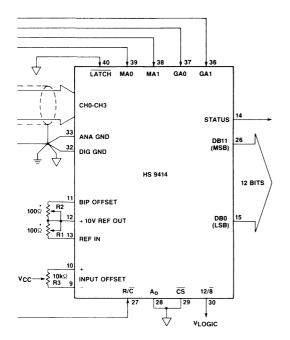

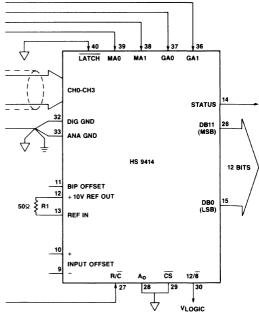

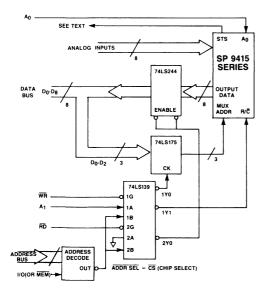

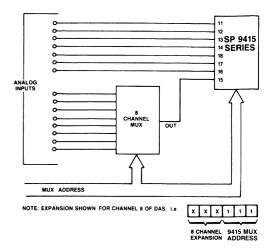

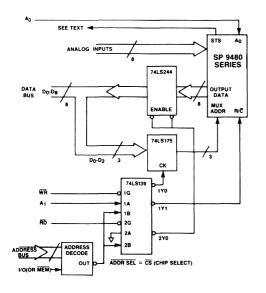

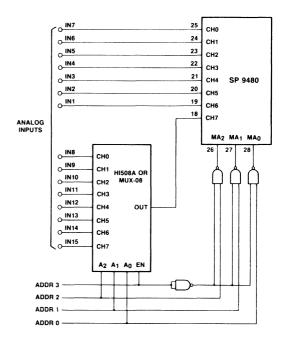

# BUILDING DATA ACQUISITION SYSTEMS WITH THE HS 9474

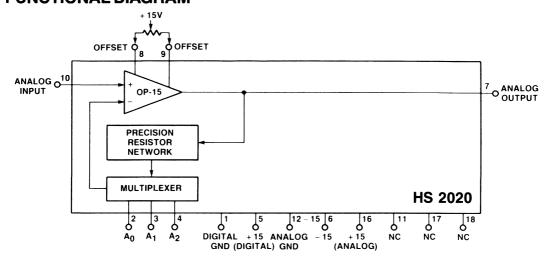

Due to the high input impedance of the HS 9474 only a single analog multiplexer is required to build a multichannel Data Acquisition System (DAS). The ON-resistance of the multiplexer can be neglected compared to the input impedance of the HS 9474. The schematic of such a DAS with eight single-ended inputs is shown in Figure 8. For differential measurements, as required when common mode voltages are superimposed on the input signal, the circuit can be expanded with a second multiplexer and an instrumentation amplifier as shown in Figure 9. The resistors R1 and R2 can be used to control the gain of the amplifier in a wide range. If it is required to change the gain from one channel to the next, small reed relays can be used to switch different resistors, one for each gain setting. But for more than two or three gain settings, the use of a digitally programmable gain amplifier is recommended. Such an amplifier is the HS 2020 which has fixed gains of 1, 2, 4, 8, 16, 32, 64 and 128. The gains can be programmed with a 3-bit binary code. Figure 10 shows the building blocks for a DAS with a very high dynamic range.

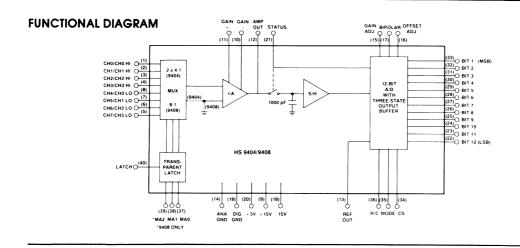

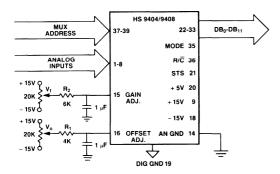

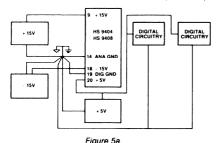

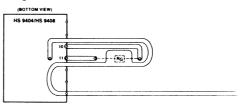

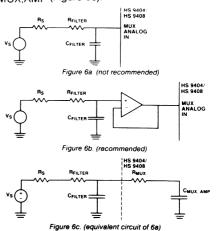

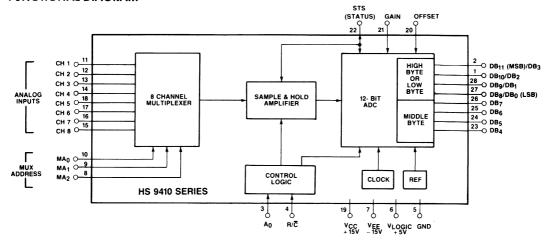

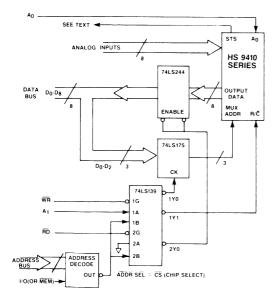

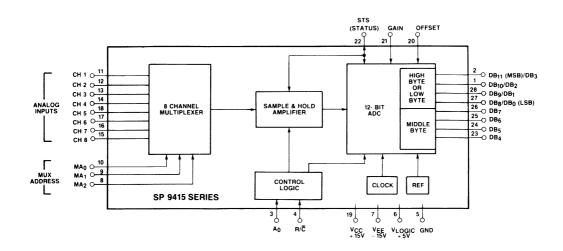

As an alternative to building a DAS with functional blocks, Hybrid Systems offers the HS 9410 series and the HS 9404/ 9408 series. These are complete DAS' as shown in Figures 8-10 packaged in one hybrid. The advantages of less board space, less inventory, simpler manufacturing and quickness to market may be beneficial to you.

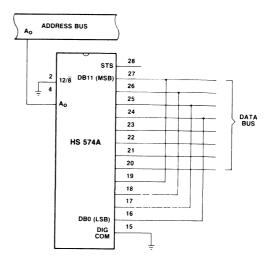

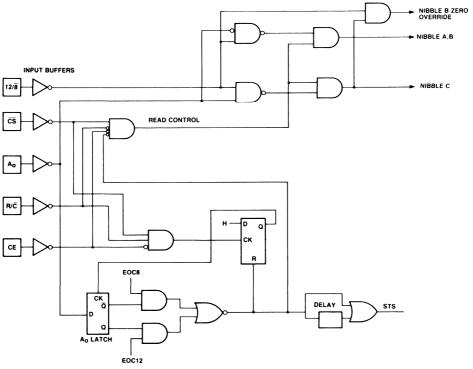

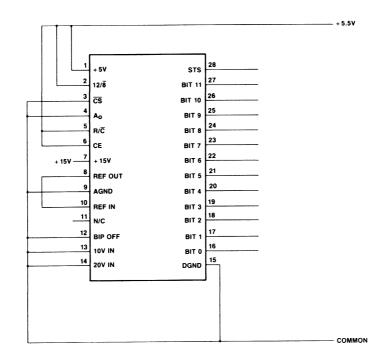

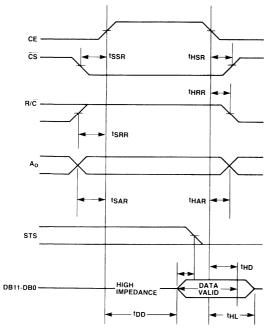

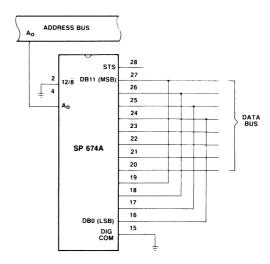

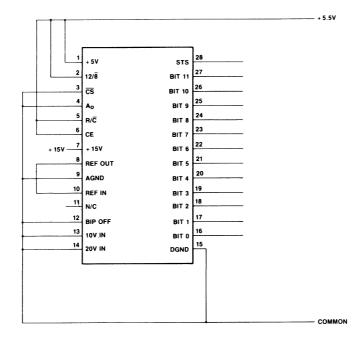

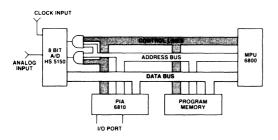

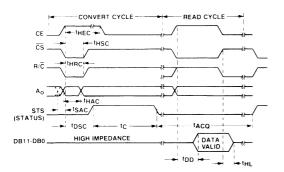

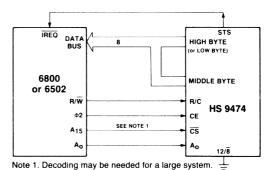

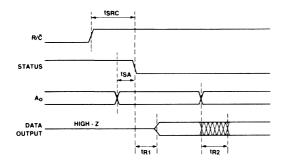

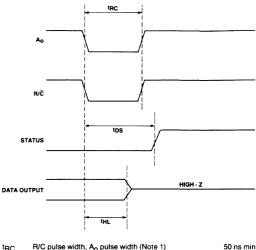

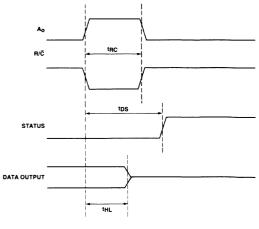

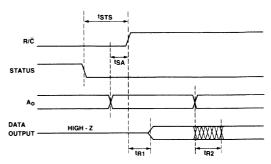

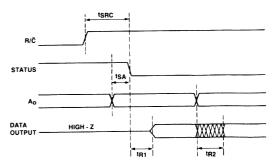

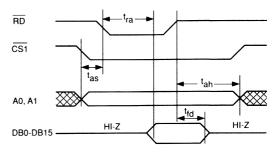

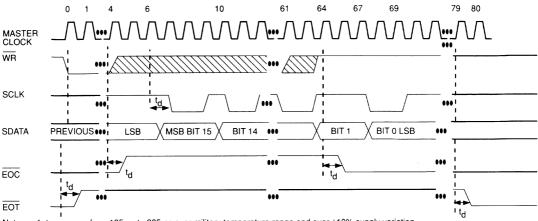

# INTERFACING THE HS 9474 TO AµP

A built-in microprocessor interface allows easy interfacing of the HS 9474 to both 8- and 16-bit microprocessor systems. The device can also be operated in a stand-alone mode. The converter provides an Ao address input which is normally connected directly to the LSB of the address bus. In memory mapped applications two adjacent memory locations are allocated to the device and from a software point of view, the HS 9474 is treated like an ordinary random access memory. Start of a conversion is achieved by writing any data byte into one of the two corresponding addresses. Depending on which of the addresses was chosen, either an 8-bit or a 12-bit conversion is started.

The STATUS-output of the converter is set to a logic high level during conversion and returns back to a low level as soon as the conversion is completed. Once a conversion is started, there are several methods to detect the end-of-conversion and to read the data. For example, the STATUS-output can be used to cause a hardware interrupt by connecting the STATUS line to the IRQ input of the processor. An interrupt service routine then can be used to read the data.

Figure 8. Block Diagram of an 8-Channel Data Acquisition System

Figure 9. Data Acquisition System with 8 Differential Channels

Figure 10. Data Acquisition System with Digitally Programmable Gain Amplifier

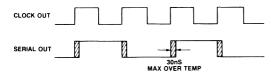

But in order to achieve the maximum conversion rate this method is not very practical because serving an interrupt requires many processor cycles (saving and restoring all register information). Another possibility is to connect the STATUS line to an input port and to read that port until conversion is completed. Also just a couple of NOP statements can be inserted in the software after the start command. The amount of the NOP commands must be chosen in accordance with the processor cycle time so that a minimum time gap of 30  $\mu$  sec is inserted between the start of conversion and the data read procedure. This method has the disadvantage that even if the converter operates at a higher speed (25  $\mu$  sec typical), the time gap must be 30  $\mu$  sec long to be within the maximum specification of the conversion time.

However, the best method to interface the HS 9474 to a processor is to suspend all processor operation during conversion. This can be done by connecting the STATUS-output to the WAIT- or HALT-input of the processor; in some cases little additional hardware such as gates or inverters is necessary. When writing the software, the data read instructions directly follow the conversion start command. As soon as a conversion is started, the processor stops operation and all bus and control lines are absolutely quiet. This greatly reduces the possibility of noise pick-up in the analog signal or the converter itself. As soon as the conversion is completed, the processor resumes operation and continues in the software to read the output data.

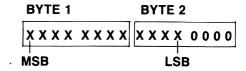

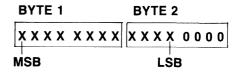

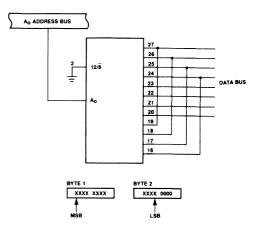

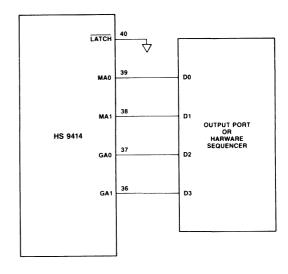

The data format can be chosen by means of the 12/8 input of the HS 9474. If this input is at logic high level, the data format is 12-bit parallel; if it is low, the data is available in two 8-bit bytes which are addressed using the  $A_{\rm O}$  line. One byte contains the upper 8 bits, while the other one contains the 4 remaining bits followed by 4 trailing zeros. The data format in the 8-bit mode is therefore left-justified.

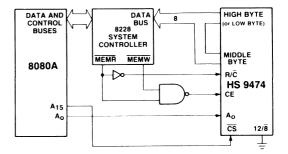

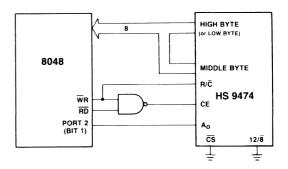

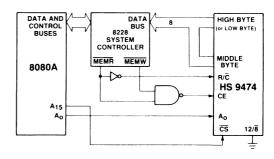

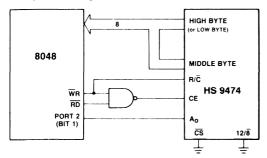

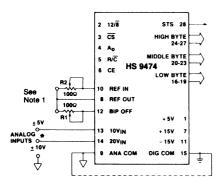

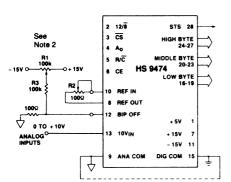

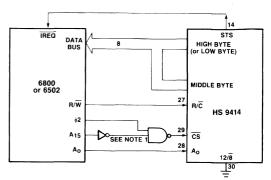

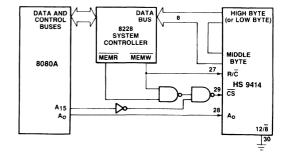

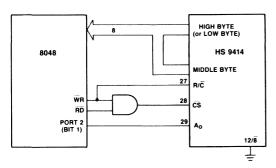

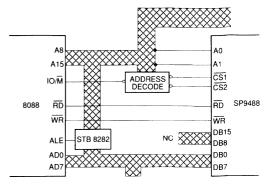

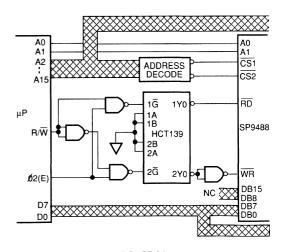

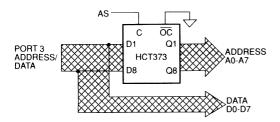

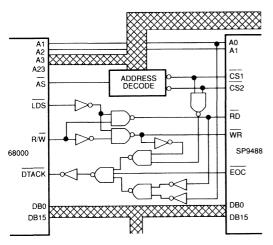

Figures 11a and 11b show how to interface the HS 9474 to the popular microprocessors 8080A and 8048. For the 8080A no address decoding is shown; depending on system complexity an address decoder might be necessary to generate the Chip-Select signal.

The data outputs of the HS 9474 are able to drive one standard TTL load. For systems where this is not sufficient, an additional bus driver (e.g., 74LS245) must be placed between the data outputs and the bus. The output buffers inside the HS 9474 are built-in CMOS technology, so pull-up resistors are not required for CMOS processor systems. The data outputs are switched into high-impedance (tri-state) if Chip-Select or Chip-Enable are not valid or the STATUS-output is logic high.

Figure 11A. Interfacing HS 9474 to 8080A µP (Top)

Figure 11B. Interfacing HS 9474 to 8048 μP (Bottom)

# **HELPFUL HINTS WHEN USING A/Ds**

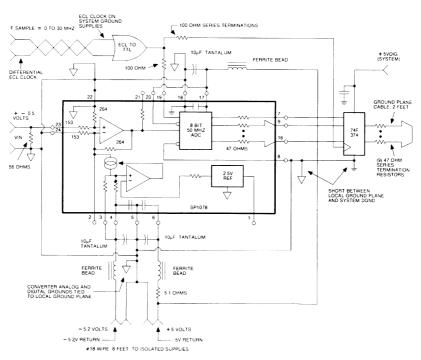

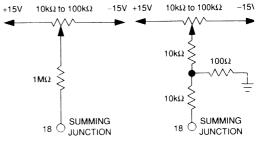

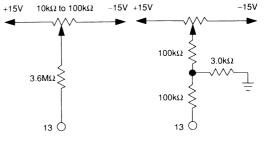

When using A/D converters, some design rules must be obeyed to achieve the desired accuracy. One should keep in mind that for 12-bit resolution and 10 volts full scale range, ½ LSB corresponds to just 1.22 mV. However, the comparator inside an ADC must be capable of making accurate decisions with much smaller voltages. In digital circuits the noise margin is in excess of a couple of hundred millivolts, but for analog circuits the noise margin is absolutely zero. Therefore, already small amounts of noise might have an effect on the ADC and this noise must be kept far away from such components.

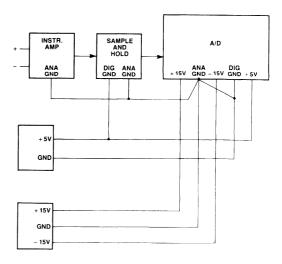

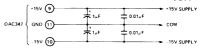

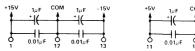

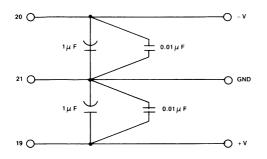

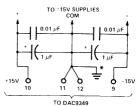

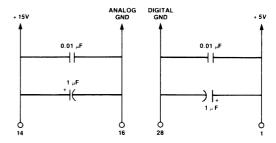

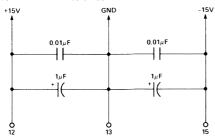

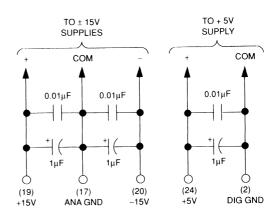

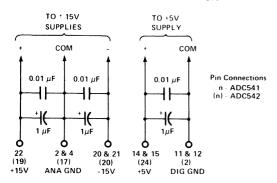

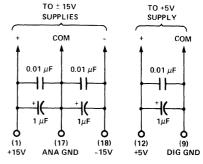

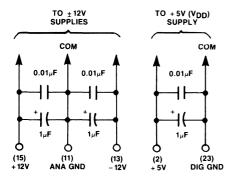

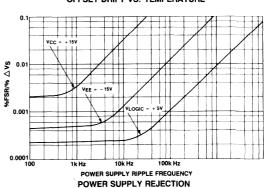

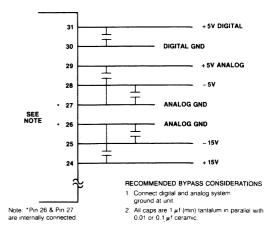

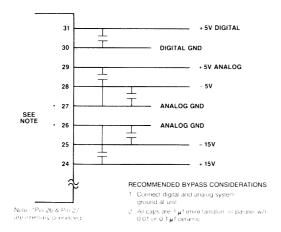

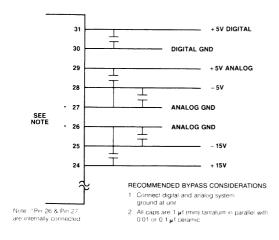

Care must be taken when selecting the power supplies. In particular, switching power supplies often have high frequency noise in excess of 100 mV on their outputs. The ability of the ADC to suppress changes in the power supply voltage is specified as Power Supply Rejection Ratio, PSRR. But this specification only applies to DC changes such as long term drift of power supply voltages. With increasing frequency the suppression of variations in voltage decreases rapidly, so that high frequency noise is not suppressed at all. If possible, the analog supply voltages of an ADC ( $\pm$ 15 volts) should be produced with linear regulated power supplies. Careful bypassing of all power supplies directly at the converter package is very important. A tantalum capacitor in parallel with a multi-layer ceramic capacitor should be used.

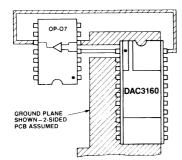

Correct layout of the ground lines is extremely important to the function of the ADC. To avoid ground loops, all ground lines of a system should be connected at one "star-point" which should be located as close to the ADC as possible. Generally, ground lines should be of very low impedance. Therefore, wide ground runs on the PC board should be used. If possible, a ground plane should be located directly underneath the converter package. This ground plane can also be used to connect analog and digital grounds. In some cases it might even be necessary to shield the converter package from the top.

However, the best protective measures are useless if the analog signal itself is superimposed with noise. In this case the input signal must be filtered and shielded cable should be used to connect the analog signal to the board.

If any problems persist while designing in a Hybrid Systems' A/D Converter, one should not hesitate to contact the factory for technical assistance. We know our product very well and our applications engineers will be able to assist in solving any problems you may have.

### **APPENDIX**

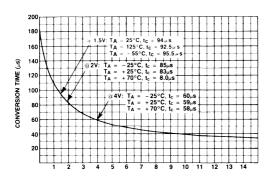

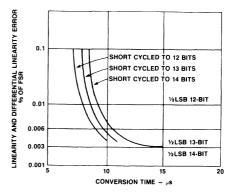

Nomogram to determine the maximum input frequency versus resolution and conversion time of ADCs without S/H amplifiers.

# QUAD S/H SOLVES ACQUISITION PROBLEMS

As users of data acquistion systems become more sophisticated and their applications become more complex, the limited capabilities of simple systems become apparent. Two new quad sample/hold amplifiers from Hybrid Systems allow circuit designers to optimally address increasingly complex data conditioning and acquisition problems.

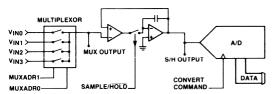

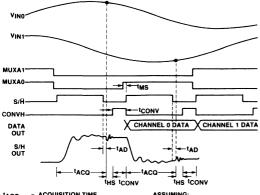

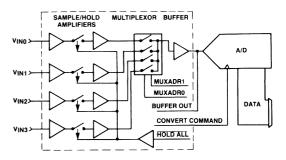

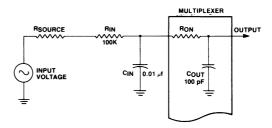

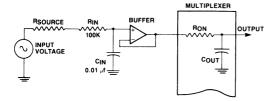

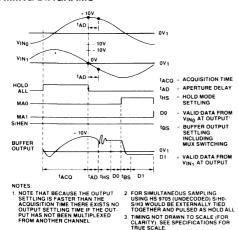

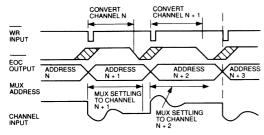

In a simple data acquisition system (DAS), the usual method of digitizing multiple inputs utilizes an input multiplexor (see Figure 1). This configuration utilizes a minimum of hardware to sequentially sample and digitize the multiple channels. The timing required is shown in Figure 1b. The time to sample any channel will consist of the sum of at least three delays. First is the acquisition time of the S/H, which is the amount of time required for a worst case input voltage swing to settle out to the required accuracy at the hold capacitor. Second would be the aperture delay time, the finite time required to actually switch the S/H into hold mode. Because this time represents a delay, it can be pipelined out

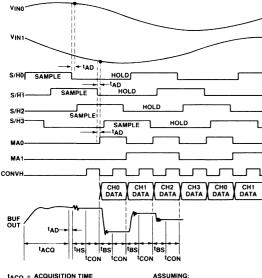

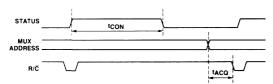

Figure 1A. Simple Sequential Four-Channel DAS

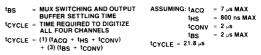

**ACQUISITION TIME** ASSUMING <sup>†</sup>ACQ = 7 μs MAX = 800 ns MAX HOLD MODE SETTLING TIME <sup>†</sup>ACQ A/D CONVERSION TIME toony APERTURE DELAY TIME tCONV = 2 µs MAX tAD = 39.2 µs tCYCLE = 39.2 μs

∴ PER CHANNEL

SAMPLING RATE = 25.5 kHz MUX SWITCHING TIME tMS TIME REQUIRED TO DIGITIZE ALL FOUR CHANNELS tCYCLE = (4) (tACQ + tHS + tCONV)

NOTE THAT TAD AND THIS HAVE BEEN PIPELINED FOR MAXIMUM SAMPLING RATE

Figure 1B. Timing

of the total time by applying the "hold" command earlier. When pipelined, the next will be the hold-mode settling time, the delay while the output buffer of the S/H settles out from the hold-mode switching transition. Third is the specified conversion time of the A/D converter. A fifth time, that for the multiplexor to switch channels, is usually pipelined to occur while the S/H is in hold mode, again not affecting the total aggregate system sampling rate.

Assigning some typical numbers to these times gives an interesting view of the efficiency of such a system. Table 1 shows that for a fast A/D converter, the large acquisition time (7  $\mu s$ ) is the bottleneck limiting a 500 kHz A/D to a 102 kHz aggregate throughput rate. Even with a slower A/D converter this time can prove to be troublesome. Consider the design of a four-channel time division multiplexor for four telephone channels. A 25  $\mu s$  A/D (40 kHz) proves too slow to sample the four channels at 8 kHz each if the prescribed 7  $\mu s$  worst-case acquisition time is allowed.

|                                                                  | Simple<br>Sequential<br>DAS | Simultaneous<br>Sampling<br>DAS | Pipelined<br>Acquisition<br>DAS |

|------------------------------------------------------------------|-----------------------------|---------------------------------|---------------------------------|

| Maximum Aggregate<br>Sampling Rate<br>(Assuming 2 µ s A/D)       | 102.0 kHz                   | 183.4 kHz                       | 250 kHz                         |

| Maximum Per Channel<br>Sampling Rate<br>(2 μ s A/D, 4-Channels)  | 25.5 kHz                    | 45.9 kHz                        | 62.5 kHz                        |

| Maximum Aggregate<br>Sampling Rate<br>(25 μ s A/D)               | 30.5 kHz                    | 35.1 kHz                        | 37.0 kHz                        |

| Maximum Per Channel<br>Sampling Rate<br>(25 μ s A/D, 4-Channels) | 7.6 kHz                     | 8.8 kHz                         | 9.3 kHz                         |

Table 1. Maximum Data Throughput Rates for Four-Channel

Data Acquisition Systems

Another characteristic of the simple DAS is the amount of stress that it applies to the S/H. The one S/H must be switched at the full conversion rate and with minimum sample-mode time to get maximum throughput. The required maximum slew rate in this configuration will be a full scale transition before adjacent conversions, even though each separate input signal must be antialias filtered to less than 1/4 of this rate (for a four-channel system). Because of the time multiplexing of the input to the sample/hold, even slowly changing signals will require maximum slew rate if one signal is near full scale and the next near negative full scale. Failure to observe maximum acquisition time specifications will lead to non-settling of the sample/hold independent of the input signal slew rate. Indeed, non-settling will show up as adjacent channel feedthrough or for worst-case situations as differential linearity aberrations near the major carry codes (for a successive approximation converter where the initial major-carry test is fooled by non-settling)

A final characteristic of the simple sequential DAS is the time delay between the samples of each channel. When time and phase relationships between the channels are important aspects of the system being monitored, these delays make the simple DAS unuseable. Consider the class of problem where multiple inputs are used to infer a multidimensional parameter of interest. A straightforward example is a robotic controller for a mechanical arm. Four channels are used to represent the x, y, z and rotational position of the arm. The instantaneous position of this arm would be very difficult to control during complex motions without simultaneous sampling of the four-dimensional vector.

Another example problem occurs during modal analysis, the testing of a structure's response to vibration. Multiple accelerometers are placed at a spacing determined by the expected maximum spatial frequency of the bending modes A calibrated impact is applied to the structure and the resulting accelerations are sampled. From the multiple channels a two- or three-dimensional map of acceleration, velocity and displacement can be generated. Any time skew in the samples will badly distort the spatial relations between the sensors and thereby distort any two- or three-dimensional reconstruction. This technique is used with finite element analysis to verify earthquake survivability of skyscrapers and the structural stability of airplanes. Other three-dimensional reconstruction techniques are used in seismic data analysis for oil exploration and earthquake studies.

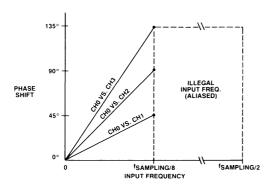

Another example of problems exists in an application where the spectra of two channels must be compared or correlated. The phase shifts between various channels are plotted versus input frequency in Figure 2. It can be shown that the time delay between the channels will apply a systematic error term of difference between the spectrums' mathematical descriptions. This shows up in the imaginary part of the spectrum as a linear slope.

Figure 2. Phase Shift Between Channels Versus Input Frequency in Four-Channel Sequential Sampling DAS (shown below)

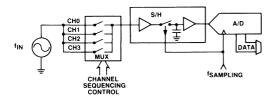

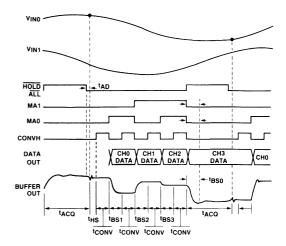

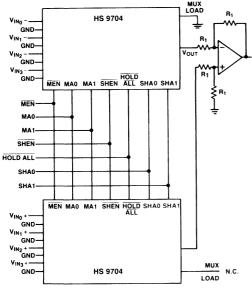

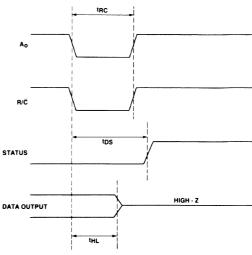

The optimal DAS architecture for these types of problems is one with a sample/hold for each channel with all channels simultaneously sampled, then converted sequentially. Figure 3 shows a simultaneous DAS architecture and timing. Notice that for an n-channel system only one acquisition time delay is required per n channels converted. A four-channel system using the same A/D converters as before yields aggregate throughputs of 183.4 kHz and 35.1 kHz, respectively (see Table 1.). Notice that the hypothetical telephone time division multiplexor is now feasible using a 25 µs A/D due to the throughput gain. Each input channel must be band limited to one quarter of the Nyquist frequency, which means that the maximum slew rates at each sample/hold will be one quarter of that in the simple sequential system. This implies that each channel will show less dynamic settling error. Finally, the samples will show time delays of less than 5 ns between each other, preserving the phase information between the channels.

Figure 3A. Simultaneous Sampling DAS Using HS 9704

$^{\circ}$  PER CHANNEL SAMPLING RATE = 45.87 kHz  $^{\circ}$  NOTE THAT  $t_{AD}$  AND  $t_{BS0}$  HAVE BEEN PIPELINED FOR MAXIMUM SAMPLING RATE

Figure 3B. Timing for Simultaneous Sampling DAS Using HS 9704

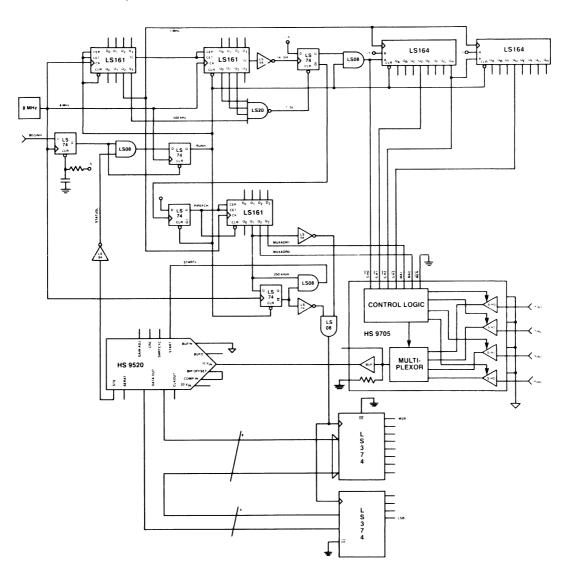

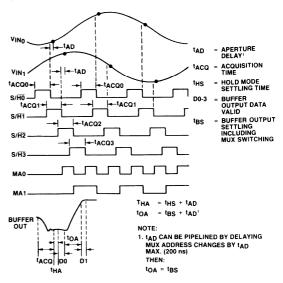

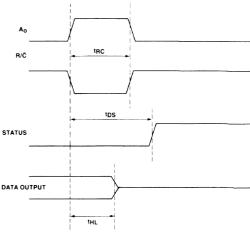

While the simultaneous sampling DAS increases throughput substantially, even more throughput can be obtained by pipelining the acquisition time entirely out of the total cycle time. A pipelined DAS and its timing is shown in Figure 4. After the pipeline is filled (11  $\mu s$  for the example in Figure 4), the system can continuously convert samples at a 250 kHz rate (assuming a 2  $\mu s$  A/D) or 37 kHz for the 40 kHz A/D (as in Table 1). Again the slew rate settling requirements upon the sample/holds are minimized, yielding better dynamic performance. The phase shift between channels is minimized, but still very significant. When maximum throughput is the design goal, a pipelined DAS makes the most sense.

Figure 4A. Pipelined Acquisition DAS Using HS 9705

taco = acquisition time

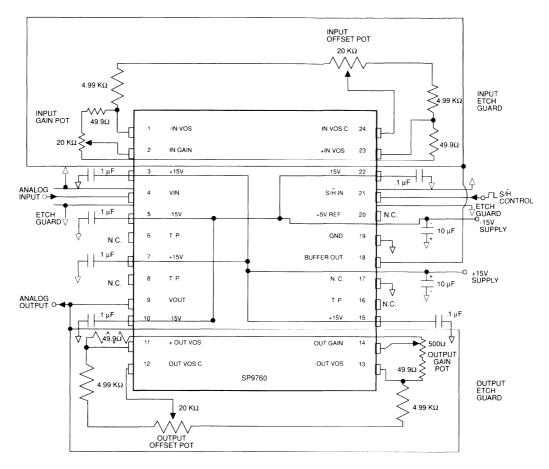

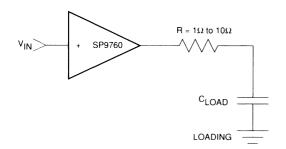

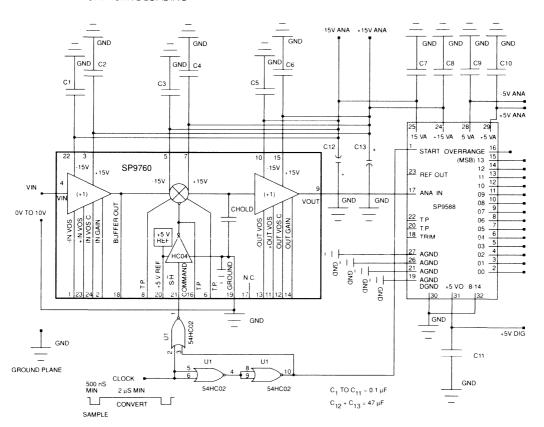

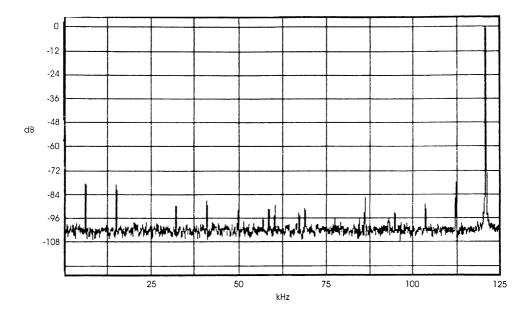

tad = aperture delay

ths = hold mode settling time

tcon = a/d conversion time

tbs = mux switching and buffer

settling time

tpipeline = taco + tad + ths + tcon

tcycle (after pipeline is full)

= t tosh

tacq = 7 µs Max tad = 200 ns Max ths = 800 ns Max tcon = 2 µs Max ts = 2 µs Max tpipeline = 10 µs tcycle = 16 µs per Channel Sampling Rate = 1/tcycle = 62.5 kHz

Figure 4B. Pipelined Sequential Data Acquisition System Using HS 9705

An interesting class of problem can be addressed by hardware identical to the pipelined system above. A fast "window grabber" system can be used to sample a limited number of points spaced much closer in time than the A/D conversion rate. For example, consider an eight-channel pipelined hardware system where each of the channels is connected to the same input. If the problem at hand involves analyzing eight points spaced 1  $\mu s$  apart (to examine the impulse response of system, for instance), it is possible to stagger the hold commands to each channel by 1  $\mu s$  to "grab" eight points with 1  $\mu s$  spacing. The multiplexor is then used to route the samples to a slow A/D to sequentially convert them in non-real time.

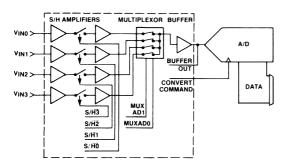

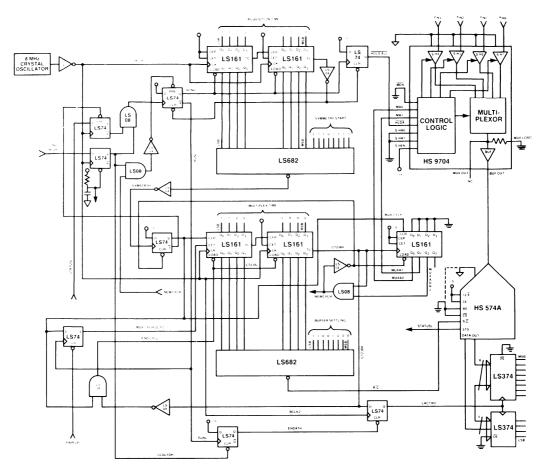

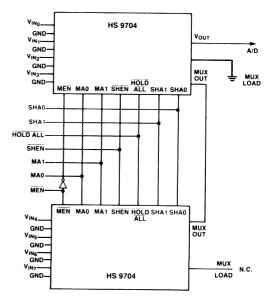

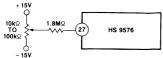

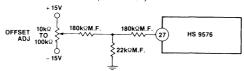

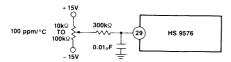

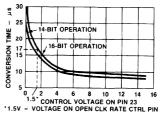

In order to support the various applications mentioned above, Hybrid Systems has announced two different versions of quad multiplexed sample/holds. The HS 9704 is a binary encoded model. Each sample/hold can be uniquely addressed by a binary address for ease in  $\mu\text{P}$  interfacing. It also supplies an overriding "hold all" single control in order to simplify the design of simultaneous S/H systems. An implementation of a simultaneous sampling system is shown in Figure 5.

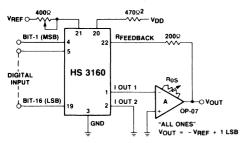

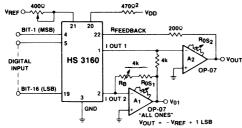

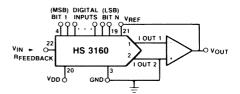

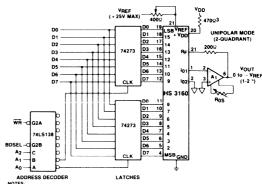

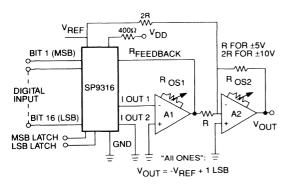

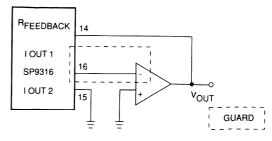

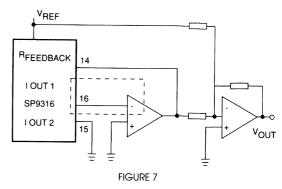

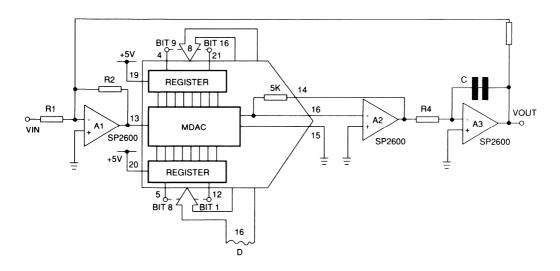

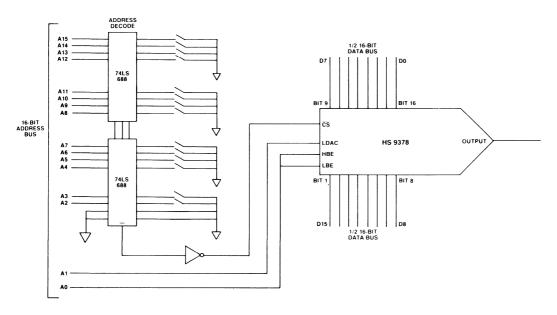

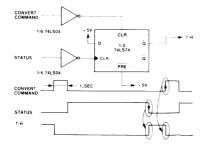

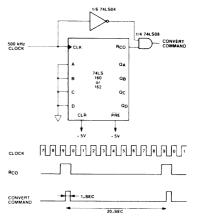

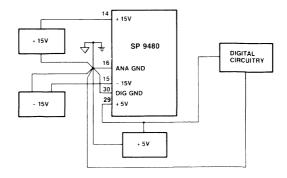

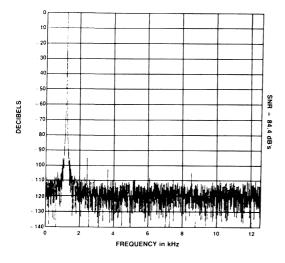

This synchronous circuit uses programmable counters to set various time delays. Converters of various speeds can be substituted by changing the programmed delays (possibly by use of dip switches) or by adjusting the master clock frequency.